# INSTRUMENTATION ENGINEERING

# ANALOG ELECTRONICS

Comprehensive Theory

with Solved Examples and Practice Questions

#### **MADE EASY Publications Pvt. Ltd.**

**Corporate Office:** 44-A/4, Kalu Sarai (Near Hauz Khas Metro Station), New Delhi-110016 | **Ph.:** 9021300500

**Email:** infomep@madeeasy.in | **Web:** www.madeeasypublications.org

# **Analog Electronics**

Copyright © by MADE EASY Publications Pvt. Ltd.

All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photo-copying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book.

**MADE EASY Publications Pvt. Ltd.** has taken due care in collecting the data and providing the solutions, before publishing this book. Inspite of this, if any inaccuracy or printing error occurs then **MADE EASY Publications Pvt. Ltd.** owes no responsibility. We will be grateful if you could point out any such error. Your suggestions will be appreciated.

# EDITIONS

First Edition: 2015

Second Edition: 2016

Third Edition: 2017

Fourth Edition: 2018

Fifth Edition: 2019

Sixth Edition: 2020

Seventh Edition: 2021

Eighth Edition : 2022

Ninth Edition: 2023

# CONTENTS

# **Analog Electronics**

# **CHAPTER 1**

| Diod | e Circuits1                                           | -84 |

|------|-------------------------------------------------------|-----|

| 1.1  | Introduction                                          | 1   |

| 1.2  | Diode Circuits : DC Analysis and Models               | 1   |

| 1.3  | Diode Logic Gates                                     | 9   |

| 1.4  | Diode Equivalent Circuits                             | 11  |

| 1.5  | DC Power Supply                                       | 14  |

| 1.6  | Rectifier                                             | 15  |

| 1.7  | Half-wave Rectifier                                   | 15  |

| 1.8  | Centre-Tapped Full-wave Rectifier                     | 25  |

| 1.9  | Bridge Rectifier                                      | 32  |

| 1.10 | Comparison of Rectifier Circuits with Resistive Load. | 36  |

| 1.11 | Filter                                                | 36  |

| 1.12 | Inductor Filter                                       | 36  |

| 1.13 | Capacitor Filter                                      | 38  |

| 1.14 | LC Filter (L-Section Filter)                          | 41  |

| 1.15 | CLC Filter (P-Section Filter)                         | 45  |

| 1.16 | Voltage Regulators                                    | 46  |

| 1.17 | Zener Diode Shunt Regulator                           | 47  |

| 1.18 | Op-amp Controlled Series Regulator                    | 49  |

| 1.19 | Transistorized Series Regulator                       | 50  |

| 1.20 | Fixed Voltage IC Regulators                           | 53  |

| 1.21 | Wave Shaping                                          | 54  |

| 1.22 | Clipper                                               | 54  |

| 1.23 | Linear Wave Shaping                                   | 61  |

| 1.24 | Clamper                                               | 68  |

| 1.25 | Voltage Multiplier                                    | 72  |

|      | Objective Brain Teasers                               | 74  |

|      | Conventional Brain Teasers                            | 80  |

# CHAPTER 2

|     | olar Junction Transistors-Characte Biasing |          |

|-----|--------------------------------------------|----------|

| 2.1 | Introduction                               | 85       |

| 2.2 | Transistors Current Components             | 87       |

| 2.3 | Early Effect                               | 91       |

| 2.4 | The Ebers-Moll (EM) Model                  | 93       |

| 2.5 | BJT Configuration                          | 95       |

| 2.6 | The Common Base Configuration              | 96       |

| 2.7 | The Common-Emitter Configuration           | 99       |

| 2.8 | The Common-Collector Configuration         | 102      |

|     | Objective Brain Teasers                    | 103      |

|     | Conventional Brain Teasers                 | 107      |

|     | APTER 3 nsistor Biasing and                |          |

|     | rmal Stabilization                         | 110 1/17 |

| Ther | mal Stabilization110-147                             |

|------|------------------------------------------------------|

| 3.1  | Introduction110                                      |

| 3.2  | The Operating Point110                               |

| 3.3  | Instability in Collector Current113                  |

| 3.4  | BJT Biasing116                                       |

| 3.5  | Fixed Bias Circuit116                                |

| 3.6  | Collector to Base Bias Circuit118                    |

| 3.7  | Self-Bias, Emitter Bias, or Voltage-Divider Bias 119 |

| 3.8  | Bias Compensation                                    |

| 3.9  | Thermal Runaway 125                                  |

| 3.10 | BJT Biasing in Integrated Circuits (ICs)130          |

| 3.11 | Constant Current Source (Basic Current Mirror) 130   |

| 3.12 | Widlar Current Source132                             |

| 3.13 | Current Repeaters134                                 |

| 3.14 | Wilson Current Source136                             |

|      | Objective Brain Teasers137                           |

|      | Conventional Brain Teasers142                        |

# **CHAPTER 4**

| BJT a | ns an Amplifier148-194                                   |

|-------|----------------------------------------------------------|

| 4.1   | Introduction148                                          |

| 4.2   | Graphical Analysis of BJT Amplifier149                   |

| 4.3   | Transistor Hybrid Model151                               |

| 4.4   | Analysis of Transistor Amplifier Circuit                 |

|       | Using h-Parameters152                                    |

| 4.5   | Small Signal Hybrid- $\Pi$ Equivalent Circuit of BJT 158 |

| 4.6   | Hybrid- $\Pi$ -Equivalent Circuit,                       |

|       | by Considering Early Effect160                           |

| 4.7   | Basic Transistor Amplifier Configurations 161            |

| 4.8   | Common-Emitter Amplifiers 162                            |

| 4.9   | Common-Collector (Emitter-Follower) Amplifier 170        |

| 4.10  | Common-Base Amplifier175                                 |

| 4.11  | Multistage Amplifiers 178                                |

|       | Objective Brain Teasers182                               |

|       | Conventional Brain Teasers                               |

|       |                                                          |

# **CHAPTER 5**

| Basic | c FET Amplifiers195-2                    | 18  |

|-------|------------------------------------------|-----|

| 5.1   | Introduction                             | 195 |

| 5.2   | The Common-Source Amplifier              | 195 |

| 5.3   | Common-Drain (Source Follower) Amplifier | 201 |

| 5.4   | The Common-Gate Configuration            | 205 |

|       | Objective Brain Teasers                  | 212 |

|       | Conventional Brain Teasers               | 215 |

# **CHAPTER 6**

| Frequ | ıency Response219-252                                                   |

|-------|-------------------------------------------------------------------------|

| 6.1   | Introduction219                                                         |

| 6.2   | Amplifier Frequency Response219                                         |

| 6.3   | Miller's Theorem                                                        |

| 6.4   | Frequency Response : BJT228                                             |

| 6.5   | High Frequency Response of Common-Emitter and Common-Source Circuits233 |

| 6.6   | High Frequency Response of Common-Base 237                              |

| 6.7   | High Frequency Response of Emitter240                                   |

|       | Objective Brain Teasers244                                              |

|       | Conventional Brain Teasers247                                           |

# CHAPTER 7

| Differential Amplifiers25 |                                  |     |  |  |  |

|---------------------------|----------------------------------|-----|--|--|--|

| 7.1                       | Introduction                     | 253 |  |  |  |

| 7.2                       | The Differential Amplifier       | 254 |  |  |  |

| 7.3                       | Basic BJT Differential Amplifier | 254 |  |  |  |

| 7.4                       | FET Differential Amplifiers      | 260 |  |  |  |

| 7.5                       | Constant Current-Bias            | 261 |  |  |  |

| 7.6                       | Level Translator                 | 264 |  |  |  |

|                           | Objective Brain Teasers          | 266 |  |  |  |

|                           |                                  |     |  |  |  |

# CHAPTER 8

| Feedl | back Amplifiers268-2                        | <u>'91</u> |

|-------|---------------------------------------------|------------|

| 8.1   | Introduction                                | 268        |

| 8.2   | Basic Feedback Concepts                     | 268        |

| 8.3   | General Block Diagram of Feedback Amplifier | 272        |

| 8.4   | Four Basic Feedback Topologies              | 275        |

| 8.5   | Series-Shunt Configuration                  | 276        |

| 8.6   | Shunt-Series Configuration                  | 278        |

| 8.7   | Series-Series Configuration                 | 280        |

| 8.8   | Shunt-Shunt Configuration                   | 281        |

| 8.9   | Summary of Results                          | 282        |

|       | Objective Brain Teasers                     | 285        |

|       | Conventional Brain Teasers                  | 289        |

# **CHAPTER 9**

| ational Amplifier                                   | .292-340     |

|-----------------------------------------------------|--------------|

| Introduction                                        | 292          |

| Block Diagram Representation of<br>A Typical Op-Amp | 292          |

| Schematic Symbol                                    | 293          |

| Operational Amplifier Characteristics               | 294          |

| DC Characteristics                                  | 294          |

| AC Characteristics                                  | 296          |

| Characteristics of Ideal Op-Amp                     | 299          |

| Ideal Voltage Transfer Curve                        | 300          |

| Inverting Amplifier                                 | 300          |

| Summing Amplifier                                   | 306          |

| Non-inverting Amplifier                             | 308          |

|                                                     | Introduction |

| 9.12  | Voltage Follower                   | 310     | 10.11 | Basic Inverting Schmitt Trigger      | 366     |

|-------|------------------------------------|---------|-------|--------------------------------------|---------|

| 9.13  | Current-to-Voltage Converter       | 311     | 10.12 | Schmitt Trigger Oscillator           | 368     |

| 9.14  | Voltage-to-Current Converter       | 312     | 10.13 | Monostable Multivibrator             | 370     |

| 9.15  | Differential Amplifier             | 313     | 10.14 | The 555 Circuit                      | 371     |

| 9.16  | Integrator and Differentiator      | 317     |       | Objective Brain Teasers              | 379     |

| 9.17  | Instrumentation Amplifier          | 319     |       |                                      |         |

| 9.18  | Log Amplifier                      | 321     | CH/   | APTER 11                             |         |

| 9.19  | Antilog or Exponential Amplifier   | 323     |       |                                      |         |

| 9.20  | Analog Multiplier IC's (Modulator) | 324     | Activ | e Filters and VCO                    | 385-418 |

| 9.21  | Analog Divider IC's (De-Modulator) | 324     | 11.1  | introduction                         | 385     |

| 9.22  | Precision Diode                    | 325     | 11.2  | Classification of Active Filters     | 385     |

| 9.23  | Half-Wave Rectifier                | 327     | 11.3  | Butterworth Filter                   | 387     |

| 9.24  | Full-Wave Rectifier                | 327     | 11.4  | Band Pass Filters                    | 392     |

|       | Objective Brain Teasers            | 329     | 11.5  | Band Stop Filter                     | 396     |

|       | Conventional Brain Teasers         | 336     | 11.6  | All Pass Filter                      | 398     |

|       |                                    |         | 11.7  | Sallen-Key (VCVS) Filters            | 404     |

| CHA   | APTER 10                           |         | 11.8  | Voltage-Controlled Oscillators       | 413     |

|       |                                    |         | 11.9  | Mathematical Model of VCOs           | 415     |

| _     | al Generators and                  |         |       |                                      |         |

| Wave  | eform Shaping Circuits             | 341-384 | CHA   | APTER 12                             |         |

| 10.1  | Introduction                       | 341     |       | 150 1 6 11 1                         |         |

| 10.2  | Oscillators                        | 341     |       | ces and Effects of Noise and         | 440 444 |

| 10.3  | The Phase-Shift Oscillator         | 344     | Inter | ference in Electronic Circuits       |         |

| 10.4  | Wien Bridge Oscillator             | 351     | 12.1  | Noise                                | 419     |

| 10.5  | LC Oscillators                     | 354     | 12.2  | Statistical Characteristics of Noise | 419     |

| 10.6  | Crystal Oscillators                | 359     | 12.3  | Representation of Noise in Circuits  | 428     |

| 10.7  | Comparison between LC Oscillators  |         | 12.4  | Noise in Single-Stage Amplifiers     |         |

|       | and Crystal Oscillators            | 361     | 12.5  | Noise in Differential Pairs          | 439     |

| 10.8  | Comparator                         | 362     | 12.6  | Noise-Power Trade-Off                | 441     |

| 10.9  | Zero-Crossing Detector             | 363     | 12.7  | Noise Bandwidth                      | 443     |

| 10.10 | Sample-And-Hold Circuits           | 365     | 12.8  | Problem of Input Noise Integration   | 443     |

**Diode Circuits**

# 1.1 INTRODUCTION

The simplest and most fundamental non-linear circuit element is a diode. Just like a resistor, the diode has two terminals; but unlike the resistor which has a linear (straight-line) relationship between the current flowing through it and the voltage appearing across it, the diode has non-linear i-v characteristics. The analysis of non-linear electronic circuits is not as straight-forward as the analysis of linear electric circuits. However, there are electronic functions that can be implemented only by non-linear circuits. Examples include the generation of dc voltages from sinusoidal voltages and the implementation of logic functions.

# 1.2 DIODE CIRCUITS : DC ANALYSIS AND MODELS

Mathematical relationships, or *models*, that describes the current-voltage characteristics of electrical elements allow us to analyze and design circuits without having to fabricate and test them in the laboratory. An example is Ohm's law, which describes the properties of a resistor. In this section, we will develop the dc analysis and modelling techniques of diode circuits.

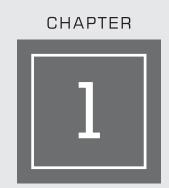

To begin to understand diode circuits, consider an *ideal diode*. It is a two terminal device having the circuit symbol and the i-v characteristics shown in figure below.

**Figure:** The ideal diode: (a) Diode circuit symbol; (b) *i-v* characteristics; (c) Equivalent circuit in the reverse direction (d) Equivalent circuit in the forward direction.

POSTAL BOOK PACKAGE 2024

The terminal characteristics of the ideal diode can be interpreted to follows:

- If a negative voltage is applied to the diode, no current flows and the diode behaves as an *open circuit* [as shown in Figure (c)]. Diodes operated in this mode are said to be *reverse biased*.

- On the other hand, if a positive current is applied to the ideal diode, zero voltage drop appears across the diode. In other words the ideal diode behaves as a **short circuit** in the forward direction [as shown in Figure (d)]. Diodes operated in this mode are said to be **forward biased**

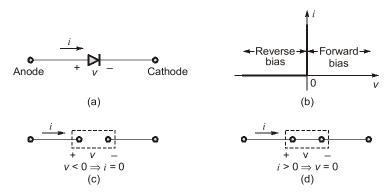

**Figure:** The two modes of operation of ideal diodes and the use of external circuit to limit (a) the forward current and (b) the reverse voltage

From the above description it should be noted that the external circuit must be designed to limit the forward current through a conducting diode, and the reverse voltage across a cut-off diode to predetermined values. Above figure shows two diode circuits that illustrate this point. In the circuit of Figure (a) the diode is obviously conducting. Thus its voltage drop will be zero, and the current through it will be determined by the  $+10\,\mathrm{V}$  supply and the  $1\,\mathrm{k}\Omega$  resistor as  $10\,\mathrm{m}A$ . The diode in the circuit is obviously cut-off, and thus its current will be zero which in turn means that the entire  $10\,\mathrm{V}$  supply will appear as reverse bias across the diode.

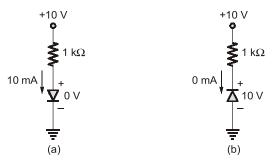

For practical diodes, *i-v* characteristics is shown as

Figure: Practical characteristics of diode

When the practical diode characteristics are compared to the ideal diode characteristics, one considers the only major difference is that, during forward biased condition. Voltage drop across the diode is 0.7 V (for silicon diode) rather than 0 V, and during reverse biased condition current flows across the diode is approximately  $I_0$  (reverse saturation current in  $\mu$ A) rather than 0 A.

#### 1.2.1 Load-Line Analysis

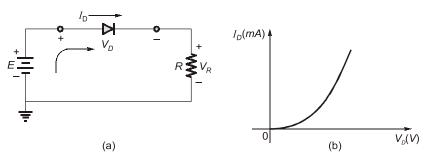

The circuit of below figure is the simplest of diode configurations. Solving the circuit is all about finding the current and voltage levels that will satisfy both the characteristics of the diode and the chosen network parameters at the same time.

Figure: Series diode configuration (a) Circuit (b) Characteristics

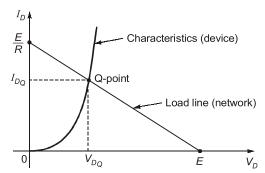

In below figure the diode characteristics are placed on the same set of axis as a straight line defined by the parameters of the network. The straight line is called a *load line* because the intersection of the vertical axis is defined by the applied load *R*. The analysis to follow is therefore called *load-line analysis*. The intersection of the two curves will define the solution for the network and define the current and the voltage levels for the network.

**Figure:** Drawing the load line and finding the point of operation

• The intersection of the load line on the characteristics of figure can be determined by applying Kirchhoff's voltage law in the clockwise direction, which results in

$$E - V_D - V_R = 0$$

or

$$E = V_D + I_D R$$

...(1.1)

- The two variables of the equation (1.1),  $V_D$  and  $I_D$ , are the same as the diode axis variables of above fig. This similarity permits plotting equation (1.1) on the same characteristics of figure.

- Set,  $V_D = 0$  V in equation (1.1)

$$E = 0 \text{ V} + I_D R$$

$$I_D = \frac{E}{R} \Big|_{V_D = 0 \text{ V}} \qquad \dots (1.2)$$

Equation (1.2) gives the magnitude of  $I_D$  on the vertical axis.

• Set,  $I_D = 0$  A in equation (1.1)

$$E = V_D + (0 \text{ A}) R$$

$$\Rightarrow E = V_D$$

$$\therefore V_D = E|_{I_D = 0 \text{ A}} \qquad \dots (1.3)$$

Equation (1.3) gives the magnitude of  $V_D$  on the horizontal axis.

• A straight line drawn between the two points will define the load line as depicted in figure. Change the level of *R* (the load), which will lead to the change in the intersection on the vertical axis. This will be resulted into the change in the slope of the load line and different point of intersection between the load line and the device characteristics.

- Now, we have a load line defined by the network and a characteristic curve defined by the device.

The point of intersection between the two is the point of operation for this circuit.

- By simply drawing a line down to the horizontal axis, we can determine the diode voltage  $V_{D_Q}$ , whereas a horizontal line from the point of intersection to the vertical axis will provide the level of  $I_{D_Q}$ . The point of operation is usually called the *quiescent point* (abbreviated "*Q-point*") to reflect its "still, unmoving" qualities as defined by a dc network.

- The solution obtained at the intersection of the two curves is the same as would be obtained by a simultaneous mathematical solution of

$$I_D = \frac{E}{R} - \frac{V_D}{R}$$

[Derived from equation 1.1] and

$$I_D = I_0(e^{V_D/\eta V_T} - 1)$$

[Diode equation]

#### 1.2.2 Series Diode Configuration

The approximate models will now be used to investigate a number of series diode configurations with do inputs. This will establish a foundation in diode analysis that will carry over into the sections and chapters to follow. The procedure described below, can infact be applied to the networks with any number of diodes in variety of configurations.

- For each configuration, firstly the state of each diode must be determined. Which diodes are "on" and which are "off"? Once determined, the appropriate equivalent can be substituted and the remaining parameters of the network can be determined.

- For the conduction region the only difference between the silicon diode and the ideal diode is the vertical shift in the characteristics, which is accounted for in the equivalent model by a dc supply of 0.7 V opposing the direction of forward current through the device. For voltages less than 0.7 V for a silicon diode and 0 V for the ideal diode the resistance is so high compared to the other elements of the network that its equivalent is the open circuit.

- In general, a diode is in the "on" state if the current established by the applied sources is such that its direction matches that of the arrow in the diode symbol, and  $V_D \ge 0$  V for ideal diode,  $V_D \ge 0.3$  V for germanium diode,  $V_D \ge 0.7$  V for silicon diode, and  $V_D \ge 1.2$  V for gallium arsenide diode.

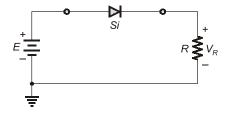

The below circuit of will be used to demonstrate the approach described in the above paragraphs.

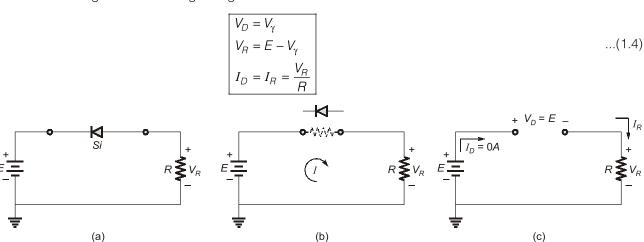

**Figure:** Series diode configuration

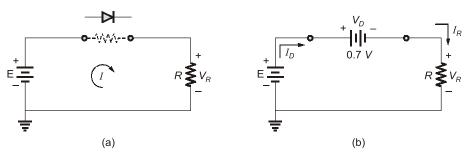

The state of the diode is first determined by mentally replacing the diode with a resistive element as shown in Figure (a). The resulting direction of I is a match with the arrow in the diode symbol, and since  $E > V_{\gamma}$  (cut-in voltage of diode), the diode is in the "on" state. The network is redrawn as shown in Figure (b) with the appropriate equivalent model for the forward biased silicon diode.

Figure: Series diode circuit analysis in forward bias

Following are the resulting voltage and current levels:

Figure: Series diode circuit analysis in reverse bias

When reverse bias is applied to diode then mentally replace the diode with a resistive element as shown in Figure (b) will reveal that the resulting current direction does not match the arrow in the diode symbol. The diode is in the "off" state, resulting in the equivalent circuit of Figure (c). Due to the open circuit, the diode current is 0 A and the voltage across the resistor R is the following:

$$V_R = I_R R = I_D R = (0 \text{ A}) R = 0 \text{ V}$$

The fact that  $V_R = 0$  V will establish E volts across the open circuit defined by Kirchhoff's voltage law. Always keep in mind that under any circumstances i.e. either DC or AC—*Kirchhoff's voltage law must be satisfied!*

#### EXAMPLE: 1.1

# [Single Branch Diode Circuits]

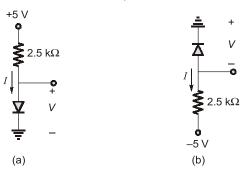

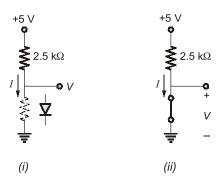

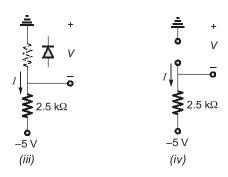

Assuming the diodes to be ideal, find the values of *I* and *V* in the circuits shown below:

6

#### **Solution:**

In Fig. (a) replacing the diode with a resistive element as shown below in *Fig. (i)*:

The resulting direction of I is a match with the arrow in the diode symbol, hence the diode is in the "on" state. Now the network can be redrawn as shown in *Fig. (ii)*.

The resulting voltage and current levels are the following:

$$V = \mathbf{0} \mathbf{V}$$

[as diode is ideal so  $V_{\gamma} = 0 \mathbf{V}$ ]

and  $I = \frac{5-0}{2.5 k} = 2 \text{ mA}$

In Fig. (b) replacing the diode with a resistive element as shown below in Fig. (iii):

Fig. (iii) reveals that the resulting direction of current *I* does not match the arrow in the diode symbol. The diode is in the "off" state resulting in the equivalent circuit as shown in *Fig. (iv)*:

Resulting current and voltage can be calculated as below:

$$I = \mathbf{0} \mathbf{A}$$

[Since diode is open circuit]

Now applying KVL in the circuit

$$V + 2.5 I - 5 = 0$$

$$\Rightarrow V + 2.5 \times 0 - 5 = 0$$

$$\Rightarrow V = 5 V$$

#### **EXAMPLE**: 1.2

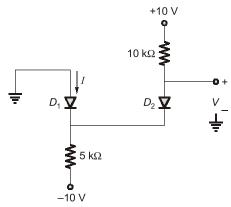

# [Multiple Branch Diode Circuit]

Assuming diodes to be ideal, find the values of *I* and *V* in the following circuit:

#### **Solution:**

In such type of circuits it might not be obvious at first sight whether none, one, or both diodes are conducting. In such cases, we make a possible assumption, proceed with the analysis, and check whether we end up with a consistent solution.

For this circuit, we shall assume that both diodes are conducting. It follow that  $V_B\!=\!0$  and  $V\!=\!0$ . The current through  $D_2$  can now be determined from

$$I_{D_2} = \frac{10-0}{10k} = 1 \text{ mA}$$

Writing a node equation at B,

$$I + 1 \text{ mA} = \frac{0 - (-10)}{5 \text{ k}}$$

$I = +1 \text{ mA}$

$\Rightarrow$

Thus  $D_1$  is conducting as originally assumed and the final result is I = 1 mA and V = 0 V.

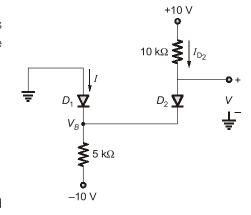

#### EXAMPLE: 1.3

Assuming diodes to be ideal, find the values of *I* and *V* in the following circuit:

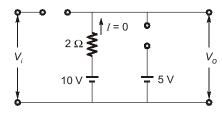

#### **Solution:**

If we assume that both diodes are conducting then  $V_B = 0$  V and V = 0 V. The current in  $D_2$  is obtained from

$$I_{D_2} = \frac{10-0}{5k} = 2 \text{ mA}$$

The node equation at B is

$$I + 2 \text{ mA} = \frac{0 - (-10)}{10 \text{ k}}$$

$$I = -1 \text{ mA}$$

I = -1 mA, is not possible as I does not match with arrow direction of the diode  $D_1$  so our original assumption is not correct. We start again, assuming that  $D_{\rm 1}$  is off and  $D_{\rm 2}$  is on. The current  $I_{D_{\rm 2}}$  is given by

$$I_{D_2} = \frac{10 - (-10)}{10 \text{ k} + 5 \text{ k}} = 1.33 \text{ mA}$$

and the voltage at node B is,  $V_B = -10 + 10 \text{ k} \times 1.33 \text{ mA} = +3.3 \text{ V}$

Thus  $D_1$  is reverse biased as assumed, and the final result is I = 0 A and V = 3.3 V.

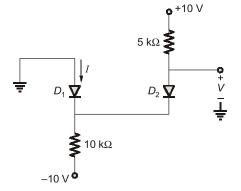

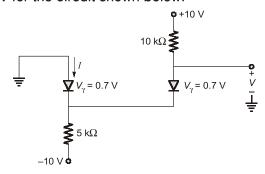

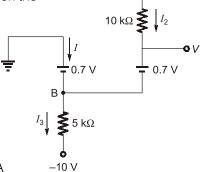

#### **EXAMPLE: 1.4**

#### [Practical diode circuit]

Find *I* and *V* for the circuit shown below:

#### Solution:

We shall assume that  $D_1$  and  $D_2$  are forward bias then the equivalent circuit can be redrawn as shown below:

So, voltage at node B is

$$V_B = -0.7 \text{ V}$$

$$V_B = -0.7 \text{ V}$$

$V = 0.7 + V_B = 0.7 - 0.7 = 0 \text{ V}$

Hence,  $I_2$  can be calculated as

$$I_2 = \frac{10 - 0}{10 \text{ k}} = 1 \text{ mA}$$

Now applying KCL at node B

$$I_3 = \frac{0.7 - (-10)}{5 \text{ k}\Omega} = 1.86 \text{ mA}$$

$I = I_3 - I_2 = 1.86 \text{ mA} - 1 \text{ mA} = 0.86 \text{ mA}$

Thus  $D_1$  is conducting as originally assumed and the final result is I = 0.86 mA and V = 0 V.

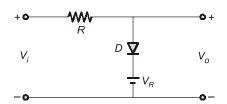

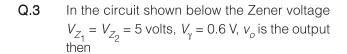

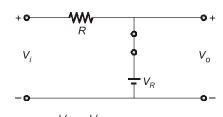

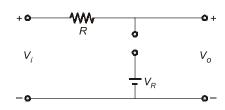

**Q.1** In the circuit shown below the input  $v_i$  has positive and negative swings and  $v_o$  is the output then

- (a)  $v_0 = 0$  for negative  $v_i$

- (b)  $v_o = V_R$  for positive  $v_i$

- (c)  $V_O = V_B$  for  $V_i > V_B$

- (d)  $v_o = V_R$  for all  $v_i$

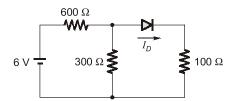

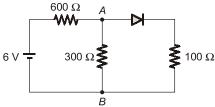

Q.2 In the *Si* diode circuit shown below, a diode current of 6.7 mA is flowing.

Assuming diode is ideal one. Its forward resistance and cut-in voltage are

- (a)  $2 \Omega$ , 0.7 V

- (b)  $0 \Omega, 0.7 V$

- (c)  $0\Omega, 0V$

- (d)  $4\Omega$ , 0V

- (a) For  $|v_i| \le 5.6$  volts,  $v_o = v_i$

- (b) For  $|v_i| \le 10$  volts,  $v_0 = v_i$

- (c) For  $|v_i| > 5.6$  volts,  $v_0 = v_i$

- (d)  $v_o = 5.6$  volts for all  $v_i$

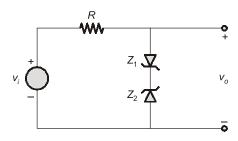

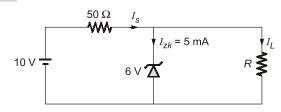

- Q.4 The 6 V Zener diode shown in figure has zero Zener resistance and a knee current of 5 mA. The minimum value of R so that the voltage across it does not fall below 6 V is

- (a)  $1200 \Omega$

- (b)  $80 \Omega$

- (c)  $50 \Omega$

- (d)  $10 \Omega$

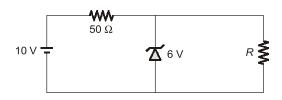

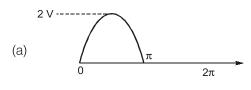

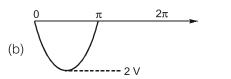

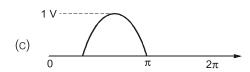

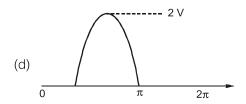

Q.5 Consider the circuit shown in Figure (I). If the diode used here has the V-I characteristic as in Figure (II), then the output waveform  $v_o$  is

- Q.6 A diode is very useful for rectifier circuits due to its

- (a) ability to conduct current only in one direction

- (b) ability to given current in both direction

- (c) zero resistance in both direction

- (d) none of these

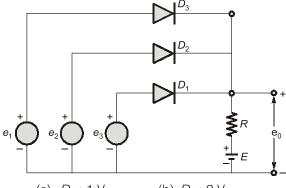

- Q.7 In the circuit shown below, if  $e_1 = 2 \text{ V}$ ,  $e_2 = 5 \text{ V}$ ,  $e_3 = 1 \text{ V}$  and E = 2 V, then which one of the diodes will be conducting and what will be the  $e_0$ ?

- (a)  $D_3: 1 V$

- (b)  $D_1: 2 V$

- (c)  $D_2:5 \text{ V}$

- (d)  $D_1:5 \text{ V}$

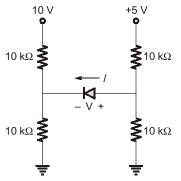

Q.8 Assuming diode in the circuit is ideal one. Find the current and voltage shown in the figure.

- (a) 0 mA, 2 V

- (b) 0 mA, -2.5 V

- (c) 1 mA, 2 V

- (d) 1 mA, 2.5 V

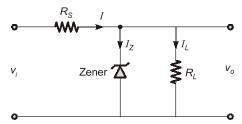

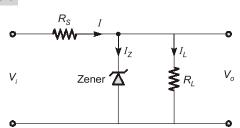

Q.9 Consider the following statements regarding the circuit given in the figure, where the output voltage is constant:

- 1.  $v_i$  > the voltage at which the Zener breaks down.

- 2.  $I_L$  < the difference between I and  $I_Z$ , the current at which the Zener breaks down.

- 3.  $R_S$  < the Zener nominal resistance.

Of these statements:

- (a) 1, 2 and 3 are correct

- (b) 1 and 2 are correct

- (c) 2 and 3 are correct

- (d) 1 and 3 are correct

- Q.10 The ideal characteristics of a voltage stabilizer is

- (a) constant output voltage with low internal resistance

- (b) constant output current with low internal resistance

- (c) constant output voltage with high internal resistance

- (d) constant internal resistance with variable output voltage

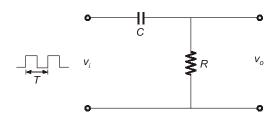

**Q.11** For the circuit given below, consider the following statements:

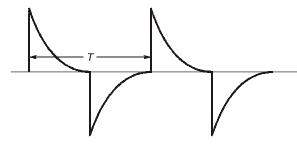

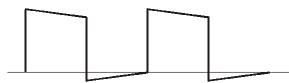

- 1. The output  $v_o$  will consist of a positive and a negative spike  $RC \ll T/2$ .

- 2. The output  $v_o$  will be similar to  $v_i$  if RC >> T/2.

- 3. The output pulse will have a higher rise time if *RC* is made progressively smaller than *T*.

Of these statements:

- (a) 1, 2 and 3 are correct

- (b) 1 and 2 are correct

- (c) 2 and 3 are correct

- (d) 1 and 3 are correct

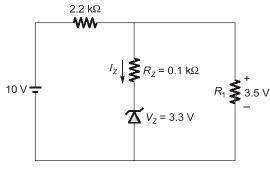

- Q.12 The current through the Zener diode in figure is

- (a) 33 mA

- (b) 3.3 mA

- (c) 2 mA

- (d) 0 mA

- Q.13 A forward biased Zener diode behaves as a

- (a) tunnel diode

- (b) Schottky diode

- (c) no diode properties

- (d) ordinary diode

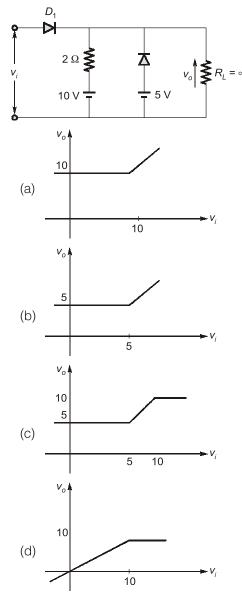

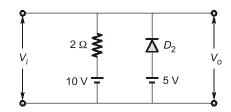

- Q.14 Assuming that diodes  $D_1$  and  $D_2$  of the circuit shown in figure to be ideal, the transfer characteristics of the circuit will be

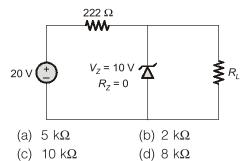

**Q.15** In the voltage regulator circuit shown below the power rating of Zener diode is 400 mW. The value of  $R_L$  that will establish maximum power in Zener diode is

#### **ANSWER KEY**

| 1. | (c) | 2. | (c) |

|----|-----|----|-----|

### **HINTS & EXPLANATIONS**

# 1. (c)

The given circuit is a positive clipper.

For  $V_i > V_{R'}$ , the diode is forward biased and acts as short-circuit.

$V_o = V_R$ For  $V_i < V_R$ , diode is reverse-biased and acts as open-circuit.

$V_{o} = V_{i}$

$$V_o = \begin{cases} V_R \text{ for } V_i \ge V_R \\ V_i \text{ for } V_i < V_R \end{cases}$$

Hence, option (c) is correct.

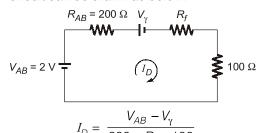

# 2. (c)

Calculating Thevenin equivalent across terminals A-B,

$$V_{AB} = \frac{6 \times 300}{300 + 600} = 2 \text{ V}$$

$$R_{AB} = \frac{600 \times 300}{600 + 300} = 200 \Omega$$

Since, the diode is forward-biased, the equivalent circuit can be drawn as below:

where,  $V_{v}$  is the cut-in voltage and  $R_{f}$  is the forward resistance of diode,

$$6.7 \times 10^{-3} = \frac{2 - V_{\gamma}}{300 + R_f}$$

The above condition is satisfied for option (c):

$$V_{v} = 0$$

and  $R_{f} = 0$

### 3. (a)

For  $V_i > V_v + V_{z_1} = 5.6 \text{ V}$ , Zener diode  $Z_1$  will be forward-bias and  $Z_2$  will be in break-down region. Hence,

$$V_{\scriptscriptstyle O} = V_{\scriptscriptstyle \Upsilon} + V_{\scriptscriptstyle Z_1} = 5.6~\mathrm{V}$$

; for  $V_i > 5.6~\mathrm{V}$

For  $V_i < -V_y - V_{Z_2} = -5.6 \text{ V}$ ,  $Z_2$  will be forward-

bias and  $Z_1$  will be in break-down region. Hence,

$$V_{_{O}} = -V_{_{Y}} - V_{_{Z_{2}}} = -5.6 \text{ V}$$

; for  $V_{i} < -5.6 \text{ V}$

For  $-5.6 \text{ V} \le V_i \le 5.6 \text{ V}$ , the reverse-biased Zener diode is not in break-down region and hence, doesn't conduct current

$$V_o = V_i \text{ for } -5.6 \le V_i \le 5.6 \text{ V}$$

$V_o = V_i \text{ for } |V_i| \le 5.6 \text{ V}$

#### 4. (b)

In the above regulator circuit,

$$I_s = \frac{10-6}{50} = 0.08 \text{ A} = 80 \text{ mA}$$

When the minimum current (knee current passes through the diode), then maximum current passes through load resistance *R*. Hence,

$$I_{L \text{ (max)}} = I_s - I_{zk}$$

$$I_{L \text{ (max)}} = 80 \text{ mA} - 5 \text{ mA}$$

$$\frac{6}{R_{s \text{ (min)}}} = 75 \times 10^{-3}$$

$$R_{s \text{ (min)}} = 80 \Omega$$

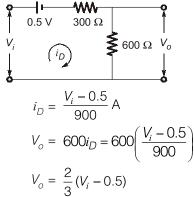

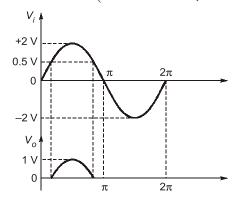

# 5. (c)

From the given V-I characteristics of diode,

$$V_{v} = 0.5 \text{ V}, R_{f} = 300 \Omega$$

In the given circuit, diode is forward-biased for  $V_i > 0.5$  V. Hence, the equivalent circuit can be drawn as below:

For  $V_i$  < 0.5 V, diode is reverse-biased and acts as open-circuit. Hence,

$$V_o = 0$$

$$V_o = \begin{cases} \frac{2}{3}(V_i - 0.5) & ; \text{ for } V_i > 0.5 \text{ V} \\ 0 & ; V_i < 0.5 \text{ V} \end{cases}$$

# 6. (a)

The diodes allows the current only in one direction and block the current flow into the other. The above property of diode is used to convert bidirectional voltage into undirectional voltage in a rectifier.

# 7. (c)

If either of diodes  $D_1$  or  $D_3$  is conducting, then  $D_2$  will also conduct and two voltages will try to superimpose at  $e_o$  which is violation of Kirchhoff's law.

When diode  $D_2$  conducts,  $e_o$  = 5 V and both the diodes  $D_1$  and  $D_3$  are reverse-biased. Hence,  $D_2$  conducts :  $e_o$  = 5 V

#### 8. (b)

Using the voltage division rule, Voltage on *n*-side of diode,

$$V_n = 10 \left( \frac{10}{10 + 10} \right) = 5 \text{ V}$$

Voltage on p-side of diode,

$$V_p = 5\left(\frac{10}{10+10}\right) = 2.5 \text{ V}$$

$V_n = 5 \text{ V} - \frac{I}{V} + \frac{V_p = 2.5 \text{ V}}{V}$

Since,  $V_n > V_p$ . Hence, the diode is reverse-biased and I = 0. The diode acts as open-circuit.

$$5 \text{ V} \bullet - V + 0 = 0.5 \text{ V}$$

$V = 2.5 - 5 = -2.5 \text{ V}$

#### 9. (b)

- 1.  $V_i = V_z + IR_s$ . Hence,  $V_i > V_z$ . Therefore, statement 1 is correct.

- **2.** We have,  $I = I_z + I_L$ Here,  $I_{L(max)} = I - I_{zk}$ , where  $I_{zk}$  is the current at which Zener break-down.

$$\begin{split} I_{L(\text{min})} &= I - I_{Z(\text{max})} \\ \text{Therefore, } I_{L} < I - I_{zk} \\ \text{Hence, statement 2 is correct.} \end{split}$$

3. The Zener nominal resistance is very small and less than the resistance  $R_{\rm s}$ . Hence, statement 3 is incorrect.

# 10. (a)

Voltage stabilizer must provide a constant output voltage.

For  $V_o \simeq V_i$ ,  $R_i$  should be very low.

Hence, the voltage stabilizer must have constant output voltage with low internal resistance.

# 11. (b)

$$V_{c} = V_{i} - V_{c}$$

$V_{o} = V_{i} - V_{c} \label{eq:voltage}$  where  $V_{c}$  is the voltage across the capacitor.

(i) If  $RC \ll T/2$ , the capacitor charges and discharges very rapidly. The output waveform consists of positive and negative spikes as shown below.

(ii) If RC >> T/2, the capacitor charges and discharges very slowly and  $V_o$  resembles  $V_i$ as shown below.

(iii) If RC is made progressively smaller than T, time constant will be small and capacitor will charge rapidly leading to a lower rise time.

Hence, only statements 1 and 2 are correct.

# 12. (c)

**BOOK PACKAGE**

We have,

$$V_o = V_z + I_z R_z$$

$3.5 = 3.3 + I_z (0.1 \times 10^3)$

$I_z = \frac{0.2}{0.1 \times 10^3} = 2 \text{ mA}$

#### 13. (d)

Zener diodes acts like normal p-n junction diodes under forward biased condition.

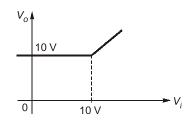

# 14. (a)

For  $V_i$  < 10 V, both the diodes are reverse-biased.

$$V_0 = 10 \text{ V}$$

For  $V_i > 10$  V, diode  $D_1$  is forward-biased and the equivalent circuit is as drawn below:

Diode  $D_2$  is reverse biased as

$$V_n > V_p$$

Hence;  $V_0 = V_i$

Transfer characteristics:

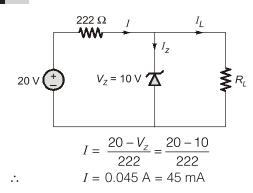

15. (b)

80

For the Zener diode,

$$P_{D(\text{max})} = 400 \,\text{mW}$$

$$\Rightarrow I_{Z(\text{max})} \cdot V_Z = 400 \,\text{mW}$$

$$I_{Z(\text{max})} = 40 \,\text{mA}$$

We have,  $I = I_{Z(\text{max})} + I_L$

$$\Rightarrow 45 \,\text{mA} = 40 \,\text{mA} + \frac{V_Z}{R_L}$$

$$\Rightarrow 5 \times 10^{-3} = \frac{10}{R_L}$$

$$\Rightarrow R_L = 2 \,\text{k}\Omega$$

# CONVENTIONAL BRAIN TEASERS

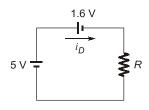

- Q.1 A light-emitting diode (LED) has a greater forward voltage drop than that of common signal diode. A typical LED can be modeled as a constant forward voltage drop  $v_D = 1.6 \text{ V}$ . Its luminous intensity  $I_v$  varies directly with forward current and is described by  $I_v = 40i_D$  millicandela (mcd).

- A series circuit consists of a LED, a current-limiting resistor R, and a 5-V DC source  $V_s$ . Find the value of R such that the luminous intensity is 1 mcd.

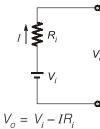

1. (Sol.)

With a 5 V DC source, LED is forward-biased and can be modelled as a constant forward voltage drop  $V_D = 1.6$  V. The equivalent circuit can be drawn as below:

$$i_D = \frac{5 - 1.6}{R}$$

The luminous intensity,  $I_V$  is defined as

$$I_V = 40i_D(mcd)$$

$$\Rightarrow 1 mcd = 40 \left( \frac{5 - 1.6}{R} \right)$$

$$\Rightarrow$$

$R = 136 \Omega$

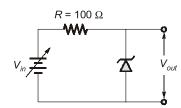

Q.2 Determine the maximum and the minimum input voltages that can be regulated by the Zener diode of circuit shown in figure. Take  $V_{\text{out}} = 5.1 \text{ V}$ , at  $I_z = 49 \text{ mA}$ ,  $I_{zk} = 1 \text{ mA}$ ,  $R_z = 7 \Omega$  at  $I_z$  power dissipation = 1 Watt.

# 2. (Sol.)

The equivalent circuit with Zener diode in breakdown region can be drawn as below:

**Given:**

$$V_{\text{out}} = 5.1 \text{ V at } I_z = 49 \text{ mA}$$

At  $I_{zk} = 1$  mA, the output voltage is

$$V_{\text{out}} = 5.1 \text{ V} - (I_z - I_{zk}) R_z$$

$V_{\text{out}} = 5.1 - (49 - 1) \times 7 \times 10^{-3}$

$V_{\text{out}} = 4.76 \text{ V}$

Hence, the minimum voltage that can be regulated is

$$V_{\text{in (min)}} = I_{zk} \times R + V_{\text{out}}$$

$V_{\text{in (min)}} = 1 \times 10^{-3} \times 100 + 4.76 = 4.86 \text{ V}$

To find the maximum input voltage, we first calculate the maximum Zener current. For power dissipation of 1 Watt,

$$I_{z(\text{max})} = \frac{P_{D(\text{max})}}{V_z} = \frac{1 \text{ W}}{5.1 \text{ V}} = 196 \text{ mA}$$

At  $I_{z(max)}$ , the output voltage is

$$V'_{\text{out}} = 5.1 \text{ V} + (I_{z(\text{max})} - I_z) R_z$$

$V'_{\text{out}} = 5.1 + (196 - 49) \times 7 = 5.1 + 1.03 = 6.13 \text{ V}$

Hence, the maximum output voltage that can be regulated is

$$V_{\text{in}(\text{max})} = I_{z(\text{max})} \cdot R + V'_{\text{out}} = 196 \times 10^{-3} \times 100 + 6.13 = 25.73 \text{ V}$$

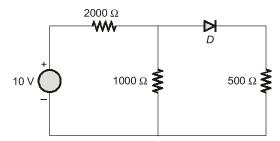

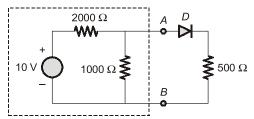

Q.3 In the circuit shown below, the diode has a forward resistance  $R_f = 15 \Omega$  and a cut-in voltage  $V_{\gamma} = 0.5 \text{ V}$ . Determine the current in the diode.

#### 3. (Sol.)

Calculating the Thevenin voltage and resistance across the terminals AB, we get,

$$V_{\text{Th}} = 10 \times \left( \frac{1000}{1000 + 2000} \right) = \frac{10}{3} \text{ V}$$

$$R_{\text{Th}} = 1000 \,\Omega \, \| 2000 \,\Omega = \frac{1000 \times 2000}{1000 + 2000} = \frac{2000}{3} \,\Omega$$