# Electronics Engineering

# **Computer Organization**

Comprehensive Theory with Solved Examples and Practice Questions

## **MADE EASY Publications Pvt. Ltd.**

Corporate Office: 44-A/4, Kalu Sarai (Near Hauz Khas Metro Station), New Delhi-110016

E-mail: infomep@madeeasy.in

Contact: 9021300500

Visit us at: www.madeeasypublications.org

# **Computer Organization**

© Copyright by MADE EASY Publications Pvt. Ltd.

All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photo-copying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book.

First Edition: 2020 Second Edition: 2021 Third Edition: 2022 Fourth Edition: 2023

© All rights reserved by MADE EASY PUBLICATIONS Pvt. Ltd. No part of this book may be reproduced or utilized in any form without the written permission from the publisher.

# **Contents**

# **Computer Organization**

| Chapt  | er 1                         | Chapt                | ter 3                                        |

|--------|------------------------------|----------------------|----------------------------------------------|

| Basics | of Computer Design3          | Instru               | ction Pipelining89                           |

| 1.1    | Computer System 3            | 3.1                  | Introduction8                                |

| 1.2    | Data Storage in the Memory11 | 3.2                  | RISC Pipelining9                             |

| 1.3    | Machine Instructions13       | 3.3                  | Pipeline Hazards9                            |

|        | Student Assignments48        | 3.4                  | Pipeline Performance Analysis11              |

|        |                              | 3.5                  | Speedup11                                    |

| Chapt  | er 2                         | Stua                 | lent Assignments11                           |

| CPU De | esign55                      |                      |                                              |

| 2.1    | Introduction55               | Chapt                | ter 4                                        |

| 2.2    | Datapath57                   | Integer and Floating |                                              |

| 2.3    | Control Unit62               | Point I              | Representation133                            |

| 2.4    | Program Interrupt80          | 4.1                  | Fixed and Floating Point Format              |

| 2.5    | Booth's Algorithm81          | 4.2                  | IEEE Floating-Point Number Representation 14 |

|        | Student Assignments84        | 4.3                  | Multiplying Floating-Point Numbers 14        |

|        |                              |                      | Student Assignments14                        |

|        |                              |                      |                                              |

# **Computer Organization**

# **Goal of the Subject**

Basic understanding of computer organization includes:

- Understanding roles of processors.

- Understanding the concept of programs as sequences of machine instructions.

- Understanding the relationship between assembly language and machine language.

- Understanding the relationship between high-level compiled languages and assembly language.

- Understanding arithmetic and logical operations

- Understanding simple data path and control designs for processors.

# Computer Organization

# INTRODUCTION

In this book we tried to keep the syllabus of Computer Organization around the GATE syllabus. Each topic required for GATE is crisply covered with illustrative examples and each chapter is provided with Student Assignment at the end of each chapter so that the students get the thorough revision of the topics that he/she had studied. This subject is carefully divided into eight chapters as described below.

- 1. Basics of Computer Design: In this chapter we discuss the Computer System, Data storage in the memory and Machine instructions

- 2. **CPU Design:** In this chapter we discuss the Datapath and Control unit design first is hardwired control unit second is microprogrammed.

- 3. Instruction Pipelining: In this chapter we discuss Performance, Instruction processing, Pipeline design and issue, Pipeline hazards, Pipeline performance analysis and Speedup.

- **4. Integer and Floating Point Representation:** In this chapter we discuss the Fixed and floating point format, IEEE floating -point number representation, Computer arithmetic, Adding 2's complement numbers and Multiplying floating-point numbers.

CHAPTER

# **Basics of Computer Design**

# 1.1 Computer System

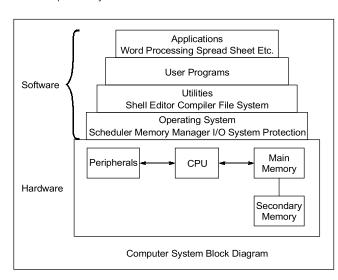

Computer system is divided into two functional entities: Hardware and Software.

- Hardware: Lowest level in a computer are all the electronic circuits and physical devices from which

it is built.

- Hardware consisting of its physical devices (CPU, memory, bus, storage devices, ...)

- Software: Sequences of instructions and data that make computers do useful work.

Software, consisting of the programs it has (Operating system, applications, utilities, ...)

Program is a sequence of instructions for a particular task.

- Operating system is set of programs included in system software package and Link between hardware and user needs.

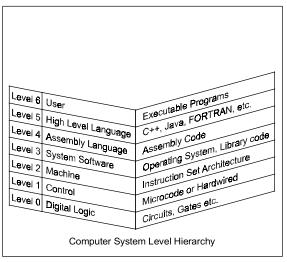

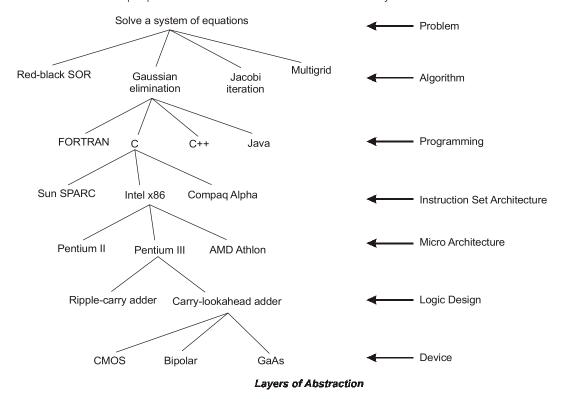

# 1.1.1 Layers of Abstraction

- Problem Statement: stated using "natural language". It may be ambiguous are imprecise.

- Algorithm: step-by-step procedure, guaranteed to finish. It is definiteness, effective computability, and finiteness.

- **Program:** Express the algorithm using a computer language such as high-level language and low-level language.

- Instruction Set Architecture (ISA): It specifies the set of instructions the computer can perform using data types and addressing modes.

- Micro-architecture: It is detailed organization of a processor implementation.

- Logic Circuits: Combine basic operations to realize micro-architecture.

- Devices: Which is properties of materials and manufacturability.

# 1.1.2 Computer Organization and Computer Architecture

**Computer design:** The determination of how to interconnect the components and which components to used based upon some specifications.

# 1.1.3 Computer Architecture (CA)

- Computer architecture is the conceptual design and fundamental operational structure of a computer system. It is a functional description of requirements and design implementations for the various parts of a computer.

- It is the science and art of selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals.

- It deals with the architectural attributes like physical address memory, CPU and how they should be designed and made to coordinate with each other keeping the goals in mind.

# 1.1.4 Computer Organization (CO)

- Computer architecture comes before computer organization.

- Computer organization is how operational attributes are linked together and contribute to realise the architectural specifications.

- It encompasses all physical aspects of computer systems e.g. Circuit design, control signals, memory types.

# 1.1.5 Computer Architecture Vs Computer Organization

Architecture and organization are independent, you can change the organization of a computer without changing its architecture.

- 1. The architecture indicates its hardware whereas the organization reveals its performance.

- 2. For designing a computer, its architecture is fixed first and then its organization is decided.

| Computer Organization                                                                                                                                             | Computer Architecture                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Computer organization deals with structural<br>relationships that are not visible to the programmer (like<br>clock frequency or the size of the physical memory). | Computer architecture deals with the functional<br>behavior of a computer system as viewed by a<br>programmer (like the size of a data type – 32 bits to an<br>integer). |  |

| A computer's organization expresses the realization of the architecture.                                                                                          | A computer's architecture is its abstract model and is<br>the programmer's view in terms of instructions,<br>addressing modes and registers.                             |  |

| Organization describes how it does it.                                                                                                                            | Architecture describes what the computer does.                                                                                                                           |  |

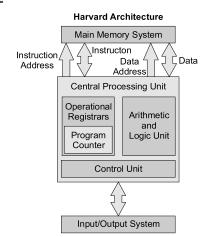

# **Von-Neumann Architecture Vs Harvard Architecture**

# Main Memory System Address Data/ Instruction Central Processing Unit Operational Registrars Program Counter Control Unit Input/Output System

# 1.1.6 Evolution of Digital Computers

| First generation: Vacuum tube computers (1945~1953)                                                                                                                                                                                                                                                                                                                                                                                                       | Second generation: Transistorized computers (1954~1965)                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Program and data reside in the same memory (stored program concepts: John von Neumann).</li> <li>Vacuum tubes were used to implement the functions (ALU &amp; CU design).</li> <li>Magnetic core and magnetic tape storage devices are used.</li> <li>Using electronic vacuum tubes, as the switching components.</li> <li>Assembly level language is used.</li> </ul>                                                                           | <ul> <li>Transistor were used to design ALU &amp; CU.</li> <li>High Level Language is used (FORTRAN).</li> <li>To convert HLL to MLL compiler were used.</li> <li>Separate I/O processor were developed to operate in parallel with CPU, thus improving the performance.</li> <li>Invention of the transistor which was faster, smaller and required considerably less power to operate.</li> </ul>                                                               |  |  |

| <b>Third generation:</b> Integrated circuit computers (1965~1980)                                                                                                                                                                                                                                                                                                                                                                                         | Fourth generation: Very large scale integrated (VLSI) computers (1980~2000)                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| <ul> <li>IC technology improved.</li> <li>Improved IC technology helped in designing low cost, high speed processor and memory modules.</li> <li>Multiprogramming, pipelining concepts were incorporated.</li> <li>DOS allowed efficient and coordinate operation of computer system with multiple users.</li> <li>Cache and virtual memory concepts were developed.</li> <li>More than one circuit on a single silicon chip became available.</li> </ul> | <ul> <li>CPU termed as microprocessor</li> <li>INTEL, MOTOROLA, TEXAS, NATIONAL semiconductors started developing microprocessor.</li> <li>Workstations, microprocessor (PC) and Notebook computers were developed.</li> <li>Interconnection of different computer for better communication LAN, MAN and WAN.</li> <li>Computational speed increased by 1000 times.</li> <li>Specialized processors like Digital Signal Processor were also developed.</li> </ul> |  |  |

| Fifth generation: System-on-chip (SOC) computers (2000~)                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| <ul> <li>E-Commerce, E- banking, home office.</li> <li>ARM, AMD, INTEL, MOTOROLA.</li> </ul>                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

High speed processor - GHz speed.

Because of submicron IC technology lot of added features in small size.

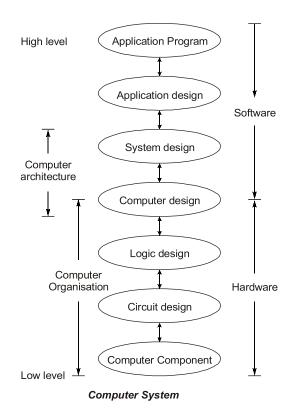

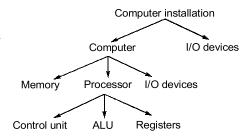

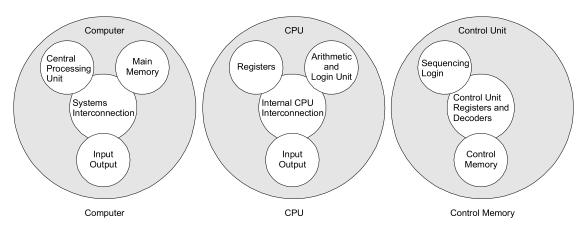

# 1.1.7 Structure and Function of a Computer System

The designer need only deal with a particular level of the system at a time. At each level, the system consists of a set of *components* and their interrelationships.

The behavior at each level depends only on a simplified, abstracted characterization of the system at the next lower level. At each level, the designer is concerned with structure and function. Important relationships are explained in the figure.

Structure is the way in which components relate to each other (shown in the following figure). Function is the operation of individual components as part of the structure. Functions are Data processing, Data storage, Data movement and Control.

Internal Structure of Computer

# 1.1.8 Components of Computer Structure

Computer Structure vs CPU Structure vs Control Unit

- 1. Input Unit: Computers can understand only machine language. Therefore for converting data from human language to machine language we use some special peripheral devices which are called input device.

- Examples: Keyboard, Mouse, Joystick, etc.

- 2. Output Unit: After passing instructions for solving particular problem, the results came out from computer comes in machine language and this is very difficult to convert that results into human language. There are several such peripheral devices which help us to convert the machine language data into human acceptable data. These devices are called output devices. *Examples:* Monitor, Printer, LCD, LED etc.

3. Memory Unit: Which is used to store data in computer.

Memory unit performs the following actions

- (a) Stores data and instructions required for processing.

- (b) Stores the intermediate results obtain during processing.

- (c) Stores final results before sending it to output unit.

Two class of storage units: (i) Primary Memory (ii) Secondary Memory

Two types of primary memory are RAM (Random Access Memory) and ROM (Read Only Memory). RAM is used to store data temporarily during the program execution. ROM is used to store data and program which is not going to change.

Secondary Memory is used for bulk storage or mass storage to store data permanently.

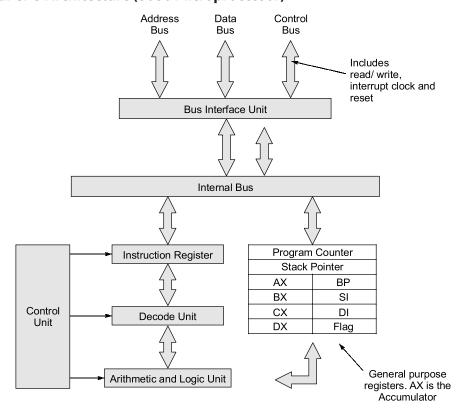

- **4. CPU:** It is main unit of the computer system. It is responsible for carrying out computational task. The major structural components of a CPU are:

- (a) Control Unit (CU): Controls the operation of the CPU and hence the computer.

- (b) Arithmetic and Logic Unit (ALU): Performs computer's data processing functions.

- (c) Register: Provides storage internal to the CPU.

- (d) CPU Interconnection: communication among the control unit, ALU, and register.

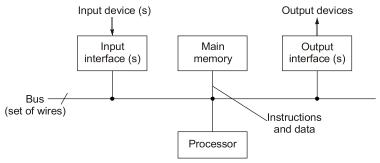

## 1.1.9 Bus Structure

**Bus:** It is a group of wires (lines or signals) which carries information from CPU to peripherals or peripherals to CPU. The CPU and Memory are connected by Data Bus, Address Bus and Control Bus.

Address Bus: It is unidirectional bus which carries address information bits form processor to peripherals.

Data Bus: It is bidirectional bus which carries data information bit form processor to peripherals and vice-versa.

**Control Bus:** It is bidirectional bus which carries control signals form processor to peripherals and viceversa.

# 1.1.10 Types of Bus Structure

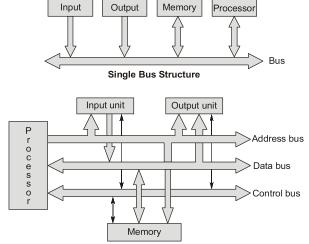

• Single bus structure: Common bus used (shown in the following figure) to communicate between peripherals and microprocessor.

Internal view of Single Bus Structure

• Two Bus Structure: One bus can be used to fetch instruction other can be used to fetch data, required for execution. It improves the performance, but cost increases.

# 1.1.11 CISC and RISC Architectures

| CISC (Complex Instruction Set Computers)                                                                           | RISC (Reduced Instruction Set Computers)                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Large instruction set                                                                                              | Compact instruction set                                                                                                                                                                                                                      |

| Instruction formats are of different lengths                                                                       | Instruction formats are all of the same length                                                                                                                                                                                               |

| Instructions perform both elementary and complex operations                                                        | Instructions perform elementary operations                                                                                                                                                                                                   |

| Control unit is micro-programmed                                                                                   | Control unit is simple and hardwired                                                                                                                                                                                                         |

| Not pipelined or less pipelined                                                                                    | Pipelined                                                                                                                                                                                                                                    |

| Single register set                                                                                                | Multiple register set                                                                                                                                                                                                                        |

| Numerous memory addressing options for operands                                                                    | Compiler and IC developed simultaneously                                                                                                                                                                                                     |

| Emphasis on hardware                                                                                               | Emphasis on software                                                                                                                                                                                                                         |

| Includes multi-clock complex instructions                                                                          | Single-clock, reduced instruction only                                                                                                                                                                                                       |

| Memory-to-memory: "LOAD" and "STORE" incorporated in instructions                                                  | Register to register: "LOAD" and "STORE" are independent instructions                                                                                                                                                                        |

| Small code sizes, high cycles per second                                                                           | Low cycles per second, large code sizes                                                                                                                                                                                                      |

| Transistors used for storing complex instructions                                                                  | Spends more transistors on memory registers                                                                                                                                                                                                  |

| Examples of CISC processors:  • VAX  • PDP?11  • Motorola 68000 family  • Intel x86 architecture based processors. | <ul> <li>Examples of RISC processors</li> <li>Apple iPods (custom ARM7TDMI SoC)</li> <li>Apple iPhone (Samsung ARM1176JZF)</li> <li>Nintendo Game Boy Advance (ARM7)</li> <li>Sony Network Walkman (Sony in house ARM based chip)</li> </ul> |

# 1.1.12 General CPU Architecture (8086 Microprocessor)

# 1.1.13 Issues of Computer Design

- Cannot assume infinite speed and memory.

- Speed mismatch between memory and processor

- Handle bugs and errors

- Multiple processors, processes, threads

- Shared memory

- Disk access

- Better performance with reduced power

# 1.1.14 Hypothetical Chip

- In the computer system data is always describe in a form of byte.

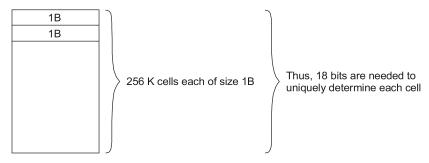

- If configuration  $4K \times 4$  is given, it implies there are  $2^{12}$  unique cells each of are 4 bits.

- Default memory configuration is byte addressable. So data is stored in the memory in the byte wise sequence. *Example:* 4 GB RAM.

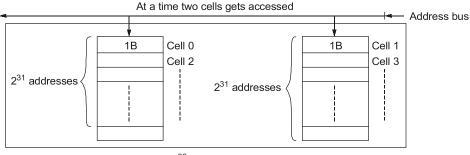

• CPU always access 1 word data. *Example:* if 1 word = 2B then at a time 2B (or 2 cell) will be accessed by the CPU and memory interfacing will be done to residue this.

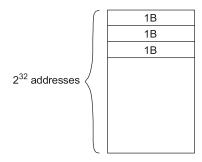

What is memory interfacing, to understand this consider main memory size is 4 GB then:

Case 1: When byte addressable with 1 W = 1B

- (i) In this case 32 bit address will be used to access data.

- (ii) CPU still will fetch 1 word at a time.

Case 2: When byte addressable with 1 word = 2B then,

Number of address bits =

$$\frac{4 \text{ GB}}{2B}$$

= 32 bit

2<sup>32</sup> addresses

- Above concept says how to access 2B at a time.

- Let's do some example to clear our understanding.

Example - 1.1 Consider 32-bit hypothetical CPU which support 256 KB memory space, system enhanced with a word addressable memory. How many address pins are saved in enhanced CPU?

## Solution:

# Initial structure of memory

By default byte addressable.

# Enhanced structure of memory

Now, the system is word addressable i.e. each cell contains 4B of data.

Note that total size of memory is constant thus,

Number of address bits =

$$\frac{256 \text{ KB}}{4B} = 16$$

Hence, 16 bits can uniquely determine each cell. Therefore, number of address pins saved 18 - 16 = 2.

2<sup>16</sup> addresses

Example-1.2 Consider 32 bit CPU which contains 28 bit address space. What is the memory capacity in byte when CPU supports.

- A. Byte addressable memory

- B. Word addressable memory

## Solution:

A. When byte addressable memory

Memory size =

$$2^{28}$$

B i.e. 256 MB

B. When word addressable memory

Memory size =

$$2^{28} \times 32$$

bit = 1 GB

### **Data Storage in the Memory** 1.2

# How to address main memory?

Main memory is a set of storage locations. Each location of memory has a unique address (a binary number starting from zero). Each "addressable" location holds a fixed number of bits. Any location can be accessed at high speed in any order (random access memory).

transfers the microprocessor's control to location 0024H. TRAP interrupts can only be masked by resetting the microprocessor. There is no other way to mask it.

**INTR:** It is level triggered and maskable interrupt. On receiving the instruction, CPU save the address of next instruction on stack and execute received instruction. It has the lowest priority. It can be disabled by resetting the microprocessor or by DI and SIM instruction.

- **Computer:** A device that accepts input, processes data, stores data, and produces output, all according to a series of stored instructions.

- **Hardware:** Includes the electronic and mechanical devices that process the data; refers to the computer as well as peripheral devices.

- **Software:** A computer program that tells the computer how to perform particular tasks.

- Computer organization: Interconnection of hardware to form the computer system

- Computer architecture: the structure and behaviour of the computer perceived by the user.

- **Input:** Whatever is put into a computer system.

- Data: Refers to the symbols that represent facts, objects, or ideas.

- **Information:** The results of the computer storing data as bits and bytes; the words, numbers, sounds, and graphics.

- Output: Consists of the processing results produced by a computer.

- **Main Memory:** Area of the computer that temporarily holds data waiting to be processed, stored, or output. *Example:* Cache and Main memory

- **Secondary Storage:** Area of the computer that holds data on a permanent basis when it is not immediately needed for processing. Example: Disk, Floppy, etc.

- Instruction set: It is a list of all the instructions, that a processor can execute.

- Addressing Modes: Specifies a rule for interpreting or modifying the address field of the instruction (before the operand is actually referenced)

- **Implied Mode:** Address of the operands are specified implicitly in the definition of the instruction. No need to specify address in the instruction.

- Immediate Mode: Instead of specifying the address of the operand, operand itself is specified.

- Register Mode: Address specified in the instruction is the register address. Designated operand need to be in a register.

- Register Indirect Mode: Instruction specifies a register which contains the memory address of the operand.

- **Direct Address Mode:** Instruction specifies the memory address which can be used directly to access the memory.

- Indirect Addressing Mode: The address field of an instruction specifies the address of a memory location that contains the address of the operand.

# Student's **Assignments**

- Q.1 What does CISC and RISC means?

- (a) common instruction set controller and rare instruction set controller

- (b) complex instruction set controller and reduced instruction set controller

- (c) compiled instruction set source code and recompiled instruction source code

- (d) none of the above

- Q.2 A 32-bit address bus allows access to a memory of capacity

- (a) 64 MB

- (b) 16 MB

- (c) 1 GB

- (d) 4 GB

- Q.3 The system bus is made up of

- (a) data bus

- (b) data bus and address bus

- (c) data bus and control bus

- (d) data bus, control bus and address bus

- Q.4 Which of the following is not involved in a memory write operation?

- (a) MAR

- (b) PC

- (c) MDR

- (d) data bus

- Q.5 The read/write line

- (a) belongs to the data bus

- (b) belongs to the control bus

- (c) belongs to the address bus

- (d) CPU bus

- Q.6 \_\_\_\_\_ is a piece of hardware that executes a set of machine-language instructions.

- (a) controller

- (b) bus

- (c) processor

- (d) motherboard

- Q.7 Given below are some statements associated with the registers of a CPU. Identify the false statement.

- (a) The program counter holds the memory address of the instruction in execution.

- (b) Only opcode is transferred to the control unit.

- (c) An instruction in the instruction register consists of the opcode and the operand.

- (d) The value of the program counter is incremented by 1 once its value has been read to the memory address register.

- Q.8 The following are four statements about Reduced Instruction Set Computer (RISC) architectures.

- 1. The typical RISC machine instruction set is small, and is usually a subset of a CISC instruction set.

- 2. No arithmetic or logical instruction can refer to the memory directly.

- 3. A comparatively large number of user registers are available.

- 4. Instructions can be easily decoded through hard-wired control units.

Which of the above statements is true?

- (a) 1 and 3 only

- (b) 1, 3 and 4 only

- (c) 1, 2 and 3 only

- (d) All of these

- Q.9 The word length of a CPU is defined as

- (a) the maximum addressable memory size

- (b) the width of a CPU register (integer or float point)

- (c) the width of the address bus

- (d) the number of general purpose CPU registers

- Q.10 Which of the following statements is false about CISC architectures?

- (a) CISC machine instructions may include complex addressing modes, which require many clock cycles to carry out.

- (b) CISC control units are typically microprogrammed, allowing the instruction set to be more flexible.

- (c) In the CISC instruction set, all arithmetic/logic instructions must be register based.

- (d) CISC architectures may perform better in network centric applications than RISC.

- **Q.11** Consider a high-level language statement i then which addressing mode is suitable for it?

- (a) autoincrement

- (b) indexed

- (c) displacement

- (d) autodecrement

- Q.12 In a 16-bit instruction code format 3 bit operation code, 12 bit address and 1 bit is assigned for address mode designation. How much data memory space is available

- (a) 4 MB

- (b) 8 KB

- (c) 2 KB

- (d) 2 GB

- Q.13 Match List-I with List-II and select the correct answer using the codes given below the lists:

- **A.** Regs[ $R_4$ ]  $\leftarrow$  Regs[ $R_4$ ] + Regs[ $R_3$ ]

- **B.** Regs[ $R_{\Delta}$ ]  $\leftarrow$  Regs[ $R_{\Delta}$ ] + 3

- **C.** Regs[ $R_4$ ]  $\leftarrow$  Regs[ $R_4$ ] + Mem[Regs[ $R_1$ ]] List-II

- 1. Immediate

- 2. Register

- 3. Register indirect

## Codes:

### Α В C

- 2 (a) 3

- (b) 2 1 3

- (c) 1 2 3

- (d) None of these

- Q.14 Relative Addressing Mode is used to write Position-Independent code because

- (a) The Code in this mode is easy to atomize

- (b) The Code in this mode is easy to make resident

- (c) The Code in this mode is easy to relocate in the memory

- (d) Code executes faster in this mode

- **Q.15** Consider an (n + k) bit instruction with a k-bit opcode and single n-bit address. Then this instruction allow \_\_\_\_\_ operations and \_addressable memory cells.

- (a)  $2^k$ ,  $2^{n+k}$

- (b)  $2^{n+k}$ ,  $2^{n+k}$

- (c)  $2^k$ ,  $2^n$

- (d)  $2^{n+k}$ ,  $2^{n+1}$

- Q.16 The register which holds the address of the location to or from which data are to be transferred is known as

- (a) index register

- (b) instruction register

- (c) memory address register

- (d) memory data register

- Q.17 Halt operation comes under \_\_\_

- (a) data transfer

- (b) control transfer

- (c) conversion

- (d) I/O transfer

- Q.18 In four-address instruction format, the number of bytes required to encode an instruction is (assume each address requires 24 bits, and 1 byte is required for operation code)

- (a) 9

- (b) 13

- (c) 14

- (d) 12

Q.19 A CPU has an arithmetic unit that adds bytes and then sets its V, C and Z flag bits as follows. The V-bit is set if arithmetic overflow occurs (in 2's complement arithmetic). The C-bit is set if a carry-out is generated from the most significant bit during an operation. The Z-bit is set if the result is zero. What are the values of the V, C and Z flag bit after 8-bit byte 1100 1100 and 1000 1111 are added?

|     | V | С | Z |

|-----|---|---|---|

| (a) | 0 | 0 | 0 |

- (b) 1 0

- (c) 1 1 1

- (d) 01 0

- Q.20 Consider the following sequence of instructions intended for execution on a stack machine. Each arithmetic operation pops the second operand, then pops the first operand, operates on them, and then pushes the result back onto the stack

| PUSH | b |

|------|---|

| PUSH | Х |

| ADD  |   |

| POP  | С |

| PUSH | С |

| PUSH | У |

| ADD  |   |

| PUSH | С |

| SUB  |   |

| POP  | Z |

Which of the following statements is/are true?

- 1. If push and pop instructions each require 5 bytes of storage, and arithmetic operations each require 1 byte of storage then the instruction sequence as a whole requires a total of 40 bytes of storage.

- 2. At the end of execution, z contains the same value as y.

- 3. At the end of execution, the stack is empty.

- (a) 1 only

- (b) 2 only

- (c) 2 and 3 only

- (d) 1 and 3 only

- Q.21 Match List-I with List-II and select the correct answer using the codes given below the lists:

List-I

List-II

- **A.** MOV X,  $R_1$  **1.** Three-address instruction

- B. STORE X

- 2. Zero-address instruction

- C. POP X

- 3. One-address instruction

- 4. Two-address instruction

# Codes:

- C Α В

- 3 2 (a) 4

- (b) 3 2 1

- (c) 2 3 4

- (d) 4 1 1

- Q.22 The register which keeps track of the execution of a program and which contains the memory address of the instruction currently being executed is known as \_\_\_\_\_

- (a) Index-Register

- (b) Memory address register

- (c) Program counter

- (d) Instruction registers

- Q.23 A certain processor executes the following set of machine instructions sequentially.

$MOV R_0$ , # 0

MOV  $R_{1}$ , 100  $(R_{0})$

ADD  $R_{1}$ , 200  $(R_{0})$

MOV 100  $(R_0)$ ,  $R_1$

Assuming that memory location 100 contains the value 35 (Hex), and the memory location 200 contains the value A4 (Hex), what could be said about the final result?

- (a) Memory location 100 contains value A4

- (b) Memory location 100 contains value DA

- (c) Memory location 100 contains value D9

- (d) Memory location 200 contains value 35

## **Answer Key:**

**1.** (d) **2.** (d)

**11.** (d) **12.** (b)

- **3.** (d)

- **4.** (b)

- **5.** (b)

- **6.** (c)

- **7.** (a)

- **8.** (d) **13.** (b)

- **9.** (b)

- **14.** (b)

- **15.** (c)

**10.** (c)

- **16.** (c) **17.** (b)

- **18.** (b)

- **19.** (b)

- **20.** (c)

- **21.** (d) **22.** (b)

- **23.** (c)

# Student's **Assignments**

**Explanations**

1. (d)

CISC: Complex instruction set controller

RISC: Reduced instruction set controller

# 2. (d)

Considering memory to be byte addressable thus, each cell is of 1B.

Number of cells =  $2^{32}$  (because address bus contains 32 bits)

$2^{32} B = 4 GB$  $\Rightarrow$

# 3. (d)

System bus is made up of data bus, address bus and control bus.

# 4. (b)

MAR is used to process address where you want

MDR it will contains the data which you want to write.

Data bus it is the path through which data flows upto memory.

# 5. (b)

The read/write line belongs to the control bus.

Processor executes set of instructions.

# 7. (a)

- (a) The program counter holds the memory address of the next instruction.

- (b) Opcode determinate the control unit.

- (c) IR register hold opcode.

- (d) Same as (a).

# 8. (d)

- RISC machine instruction set is small and of fixed length.

- No arithmetic or logical instruction can refer to memory directly because it will slowdown its speed. Registers are used to perform arithmetic and logical functions.

- Large number of user registers available because there is no hindrance of costs. Speed is the main motive.

- Instructions are easily decoded since logic gates are used.

# 9. (b)

Word length of a CPU depends on number of data lines (or width of a CPU registers).

# 10. (c)

CISC (Complex Instruction Set computers) as the name says uses complex addressing

modes to enhance the performance with limited resources.

- CISC control units are typically microprogrammed. So that any changes made are easily acceptable.

- In the CISC, arithmetic or logical instructions may be memory based.

# 11. (d)

i- is auto decrement instruction.

**Example:** store  $i \rightarrow R_1$  $(R_1)$  – will give i - -

# 12. (b)

| Opcode | Address | Mode  |

|--------|---------|-------|

| 3 bit  | 12 bit  | 1 bit |

Data memory space =  $2^{12} \times 16$  bit =  $2^{12} \times 2B = 8$  KB

# 13. (b)

(a)  $R_4 \leftarrow R_4 + R_3$

Register address in mode semi, operand is directly fetched from registers.

(b)

$$R_4 \leftarrow R_4 + \boxed{3}$$

Immediate value

Immediate addressing modes.

(c)  $R_4 \leftarrow R_4 + \text{Mem}[\text{Regs}[R_1]]$  register indirect

# 14. (b)

The code is this mode is easy to relocate in the memory by using offset value.

# 15. (c)

- k-bit opcode means  $2^k$  operations.

- *n*-bit address means 2<sup>n</sup> addressable memory cells.

# 16. (c)

Memory address register is used to hold the address from which or to which data are to be transferred.

# 17. (b)

Halt operation comes under control transfer instruction.

# 18. (b)

4-address instruction format each address byte of 24 bits

$\Rightarrow$  4-address = 24  $\times$  4 = 96 bits and 1B for operation code.

in bytes =

$$\frac{96}{8} + 1$$

= 12 + 1 = 13 bytes

# 19. (b)

V-bit ⇒ overflow bit

C-bit  $\Rightarrow$  carry bit

Z-bit  $\Rightarrow$  zero bit

$$= 111 + 000 = 1 \Rightarrow V-bit$$

And since result  $\neq 0$  then Z-bit = 0

V C Z

1 1 0

# 20. (c)

- 1. PUSH b

- 2. PUSH x

- 3. ADD

- 4. POP c

- 5. PUSH c

- 6. PUSH y

- 7. ADD

- 8. PUSH c

- 9. SUB

- 10.POP z

- (a) Push and Pop  $\rightarrow$  5B

Arithmetic → 1B

Total =  $7(Push/Pop) \times 5B + 3(arithmetic) \times 1$ = 35 + 3 = 38B

Hence, 1 statement is false.