# **GATE**2025

## **Electronics Engineering**

- ✓ Fully solved with explanations

- Analysis of previous papers

- Topicwise presentation

- ▼ Thoroughly revised & updated

#### **MADE EASY Publications Pvt. Ltd.**

Corporate Office: 44-A/4, Kalu Sarai (Near Hauz Khas Metro Station), New Delhi-110016 | Ph.: 9021300500

**Email:** infomep@madeeasy.in | **Web:** www.madeeasypublications.org

## GATE - 2025 Electronics Engineering

Topicwise Previous GATE Solved Papers (1995-2024)

#### Editions

1st Edition : 2007 2<sup>nd</sup> Edition : 2008 3<sup>rd</sup> Edition : 2009 4<sup>th</sup> Edition : 2010 5<sup>th</sup> Edition : 2011 6<sup>th</sup> Edition : 2012 7<sup>th</sup> Edition : 2013 8<sup>th</sup> Edition : 2014 9<sup>th</sup> Edition : 2015 10<sup>th</sup> Edition : 2016 11<sup>th</sup> Edition : 2017 12<sup>th</sup> Edition : 2018 13<sup>th</sup> Edition : 2019 14<sup>th</sup> Edition : 2020 15<sup>th</sup> Edition : 2021 16<sup>th</sup> Edition : 2022 17<sup>th</sup> Edition : 2023

18th Edition : 2024

© Copyright, by **MADE EASY Publications Pvt. Ltd.**All rights are reserved. No part of this publication may be reproduced, stored in or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photo-copying, recording or otherwise), without the prior written permission of the above mentioned publisher of this book.

**MADE EASY Publications Pvt. Ltd.** has taken due care in collecting the data and providing the solutions, before publishing this book. Inspite of this, if any inaccuracy or printing error occurs then **MADE EASY Publications Pvt. Ltd.** owes no responsibility. We will be grateful if you could point out any such error. Your suggestions will be appreciated.

## Preface

Over the period of time the GATE examination has become more challenging due to increasing number of candidates. Though every candidate has ability to succeed but competitive environment, in-depth knowledge, quality guidance and good source of study is required to achieve high level goals.

The new edition of **GATE 2025 Solved Papers : Electronics Engineering** has been fully revised, updated and edited. The whole book has been divided into topicwise sections.

At the beginning of each subject, analysis of previous papers are given to improve the understanding of subject.

I have true desire to serve student community by way of providing good source of study and quality guidance. I hope this book will be proved an important tool to succeed in GATE examination. Any suggestions from the readers for the improvement of this book are most welcome.

B. Singh (Ex. IES)

Chairman and Managing Director

MADE EASY Group

## **GATE-2025**

### **Electronics Engineering**

## **CONTENTS**

| 1.  | Network Theory1 - 7                                |

|-----|----------------------------------------------------|

| 2.  | Electromagnetics79 - 14                            |

| 3.  | Control Systems146 - 22                            |

| 4.  | Electronic Devices and Circuits223 - 27            |

| 5.  | Analog Circuits274 - 37                            |

| 6.  | Digital Circuits and Computer Organization372 - 43 |

| 7.  | Signals and Systems440 - 51                        |

| 8.  | Communication Systems513 - 59                      |

| 9.  | Engineering Mathematics597 - 66                    |

| 10. | General Aptitude666 - 71                           |

## Network Theory

# UNIT

## CONTENTS

| 1. | Basics of Network Analysis | 3 |

|----|----------------------------|---|

| ١. | Basics of Network Analysis | ( |

- 2. Sinusoidal Steady State 20

- 3. Network Theorems 35

- 4. Transient Analysis 45

- 5. Two Port Networks 61

- 6. Graph Theory and State Equations 73

- 7. Network Functions 75

## Network Theory

## Syllabus

Circuit analysis: Node and mesh analysis, superposition, Thevenin's theorem, Norton's theorem, reciprocity. Sinusoidal steady state analysis: phasors, complex power, maximum power transfer. Time and frequency domain analysis of linear circuits: RL, RC and RLC circuits, solution of network equations using Laplace transform. Linear 2-port network parameters, wye-delta transformation.

#### **Analysis of Previous GATE Papers**

| Exam<br>Year | 1 Mark<br>Ques. | 2 Marks<br>Ques. | 3 Marks<br>Ques. | Total<br>Marks |

|--------------|-----------------|------------------|------------------|----------------|

| 1995         | 8               | _                | _                | 8              |

| 1996         | 3               | 1                | I                | 5              |

| 1997         | 4               | 2                | 1                | 11             |

| 1998         | 6               | _                | 1                | 6              |

| 1999         | 2               | 3                | 1                | 8              |

| 2000         | 3               | 2                | 1                | 7              |

| 2001         | 3               | 4                | ı                | 11             |

| 2002         | 2               | 2                | 1                | 6              |

| 2003         | 4               | 8                | -                | 20             |

| 2004         | 5               | 5                | -                | 15             |

| 2005         | 5               | 6                | ı                | 17             |

| 2006         | 6               | _                | 1                | 6              |

| 2007         | 2               | 4                | -                | 10             |

| 2008         | 2               | 7                | 1                | 16             |

| 2009         | 3               | 4                |                  | 11             |

| 2010         | 2               | 4                | _                | 10             |

| 2011         | 3               | 3                | _                | 9              |

| 2012         | 4               | 4                | _                | 12             |

| 2013         | 3               | 6                | _                | 15             |

| Exam<br>Year | 1 Mark<br>Ques. | 2 Mark<br>Ques. | Total<br>Marks |

|--------------|-----------------|-----------------|----------------|

| 2014 Set-1   | 2               | 4               | 10             |

| 2014 Set-2   | 2               | 2               | 6              |

| 2014 Set-3   | 2               | 4               | 10             |

| 2014 Set-4   | 2               | 4               | 10             |

| 2015 Set-1   | 4               | 3               | 10             |

| 2015 Set-2   | 3               | 3               | 9              |

| 2015 Set-3   | 3               | 2               | 7              |

| 2016 Set-1   | 1               | 2               | 5              |

| 2016 Set-2   | 4               | 3               | 10             |

| 2016 Set-3   | 1               | 3               | 7              |

| 2017 Set-1   | 1               | 2               | 5              |

| 2017 Set-2   | 2               | 2               | 6              |

| 2018         | 1               | 3               | 7              |

| 2019         | 1               | 2               | 5              |

| 2020         | 3               | 2               | 7              |

| 2021         | 2               | 4               | 10             |

| 2022         | 2               | 3               | 8              |

| 2023         | 4               | 1               | 6              |

| 2024         | 2               | 2               | 6              |

## **Basics of Network Analysis**

- Two 2 H inductance coils are connected in series and are also magnetically coupled to each other the coefficient of coupling being 0.1. The total inductance of the combination can be

- (a) 0.4 H

- (b) 3.2 H

- (c) 4.0 H

- (d) 4.4 H

[1995:1 M]

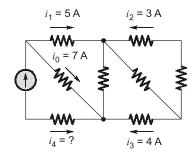

**1.2** The current  $i_A$  in the circuit of figure is equal to

- (a) 12 A

- (b) -12 A

- (c) 4 A

- (d) None of these

[1997:1 M]

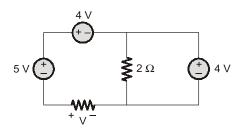

The voltage V in figure is equal to

- (a) 3 V

- (b) -3 V

- (c) 5 V

- (d) None of these

[1997:1 M]

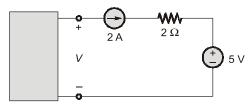

The voltage V in figure is always equal to

- (a) 9 V

- (b) 5 V

- (c) 1 V

- (d) None of these

[1997:1 M]

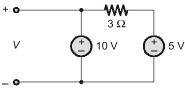

**1.5** The voltage *V* in figure is

- (a) 10 V

- (b) 15 V

- (c) 5 V

- (d) None of the these

[1997:1 M]

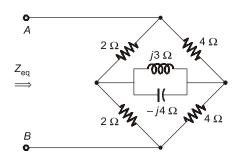

**1.6** In the circuit of Fig. the equivalent impedance seen across terminals A, B is

- (a)  $(16/3) \Omega$

- (b)  $(8/3) \Omega$

- (c)  $(8/3 + 12 i) \Omega$

- (d) None of the above

[1997:2 M]

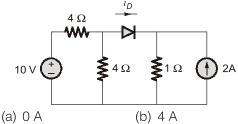

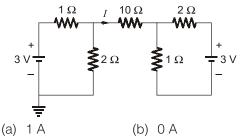

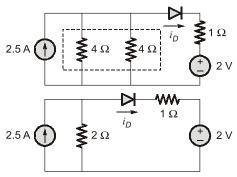

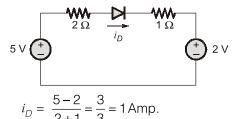

In the circuit shown in the figure the current  $i_D$ through the ideal diode (zero cut in voltage and zero forward resistance) equals

- (c) 1 A

- (d) None of these

[1997 : 3 Marks]

- The nodal method of circuit analysis is based on

- (a) KVL and Ohm's law

- (b) KCL and Ohm's law

- (c) KCL and KVL

- (d) KCL, KVL and Ohm's law

[1998:1 M]

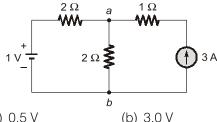

The voltage across the terminals a and b in Fig. is

(a) 0.5 V

4

- (b) 3.0 V

- (c) 3.5 V

- (d) 4.0 V

[1998:1 M]

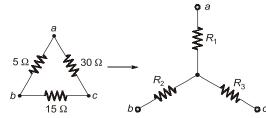

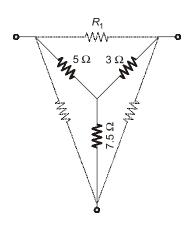

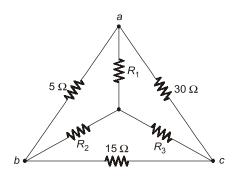

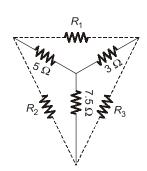

1.10 A Delta-connected network with its Wye-equivalent is shown in the figure. The resistances  $R_1$ ,  $R_2$  and  $R_3$  (in ohms) are respectively

- (a) 1.5, 3 and 9

- (b) 3, 9 and 1.5

- (c) 9, 3 and 1.5

- (d) 3, 1.5 and 9

[1999: 2 M]

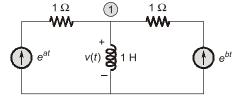

**1.11** In the circuit of the figure, the voltage v(t) is

- (a)  $e^{at} e^{bt}$

- (b)  $e^{at} + e^{bt}$

- (c)  $ae^{at} be^{bt}$

- (d)  $ae^{at} + be^{bt}$

[2000:1 M]

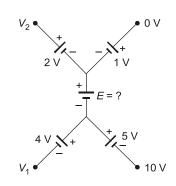

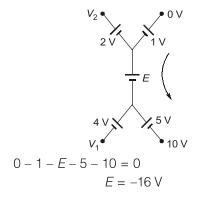

1.12 In the circuit of the figure, the value of the voltage source E is

- (a) -16 V

- (b) 4 V

- (c) -6 V

- (d) 16 V

[2000:1 M]

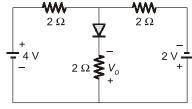

**1.13** For the circuit in the figure, the voltage  $V_0$  is

- (a) 2 V

- (b) 1 V

- (c) -1 V

- (d) None of these

[2000:2 M]

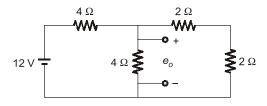

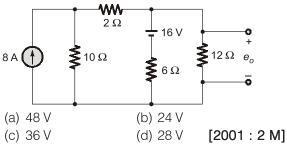

The voltage  $e_o$  in the figure is

- (a) 2 V

- (c) 4 V

- (d) 8 V

[2001:1 M]

- 1.15 If each branch of a Delta circuit has impedance  $\sqrt{3}$  Z, then each branch of the equivalent Wye circuit has impedance.

- (c)  $3\sqrt{3} Z$

- (d)  $\frac{Z}{2}$

[2001:1 M]

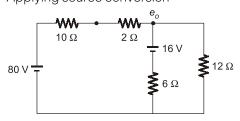

**1.16** The voltage  $e_o$  in the figure is

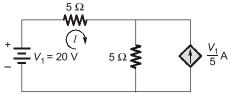

The dependent current source shown in the figure

- (a) delivers 80 W

- (b) absorbs 80 W

- (c) delivers 40 W

- (d) absorbs 40 W

[2002:1 M]

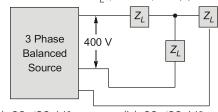

**1.18** If the 3-phase balanced source in the figure delivers 1500 W at a leading power factor 0.844, then the value of  $Z_l$  (in ohm) is approximately

- (a) 90∠32.44°

- (b) 80∠32.44°

- (c) 80∠-32.44°

- (d) 90∠-32.44°

[2002:2 M]

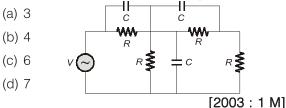

**1.19** The minimum number of equations required to analyze the circuit shown in the figure is

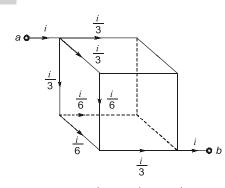

**1.20** Twelve 1  $\Omega$  resistances are used as edges to form a cube. The resistance between two diagonally opposite corners of the cube is

- (a)  $\frac{5}{6}\Omega$

- (b) 1  $\Omega$

- (c)  $\frac{6}{5}\Omega$

- (d)  $\frac{3}{2}\Omega$

[2003 : 2 M]

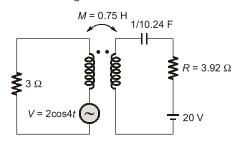

**1.21** The current flowing through the resistance *R* in the circuit in the figure has the form *P* cos 4*t*, where *P* is

- (a) (0.18 + i0.72)

- (b) (0.46 + i1.90)

- (c) -(0.18 + i 1.90)

- (d) -(0.192 + j0.144)

[2003:2 M]

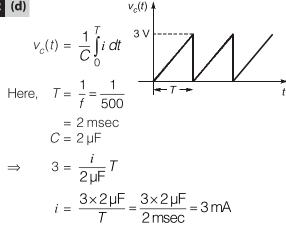

1.22 An ideal sawtooth voltage waveform of frequency 500 Hz and amplitude 3 V is generated by charging a capacitor of 2 μF in every cycle. The charging requires

- (a) constant voltage source of 3 V for 1 ms.

- (b) constant voltage source of 3 V for 2 ms.

- (c) constant current source of 3 mA for 1 ms.

- (d) constant current source of 3 mA for 2 ms.

[2003:2 M]

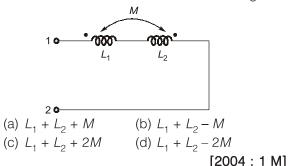

**1.23** The equivalent inductance measured between the terminals 1 and 2 for the circuit shown in the figure is

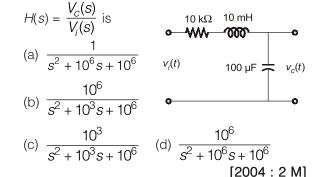

**1.24** For the circuit shown in the figure, the initial conditions are zero. Its transfer function

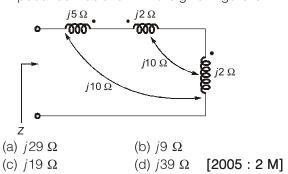

**1.25** Impedance Z as shown in the given figure is

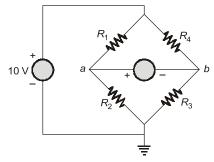

**1.26** If  $R_1 = R_2 = R_4 = R$  and  $R_3 = 1.1 R$  in the bridge circuit shown in the figure, then the reading in the ideal voltmeter connected between a and b is

- (a) 0.238 V

- (b) 0.138 V

- (c) -0.238 V

- (d) 1 V

[2005 : 2 M]

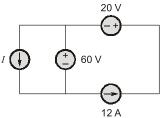

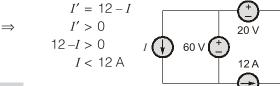

1.27 In the interconnection of ideal sources shown in the figure, it is known that the 60 V source is absorbing power.

Which of the following can be the value of the current source I?

- (a) 10 A

- (b) 13 A

- (c) 15 A

- (d) 18 A

- [2009: 1 M]

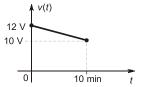

**1.28** A fully charged mobile phone with a 12 V battery is good for a 10 minute talk-time. Assume that, during the talk-time the battery delivers a constant current of 2 A and its voltage drops linearly from 12 V to 10 V as shown in the figure. How much energy does the battery deliver during this talk-time?

- (a) 220 J

- (b) 12 kJ

- (c) 13.2 kJ

- (d) 14.4 J

[2009:1 M]

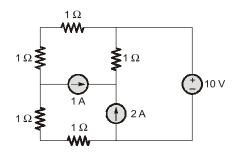

1.29 In the circuit shown, the power supplied by the voltage source is

- (a) 0 W

- (b) 5 W

- (c) 10 W

(d) 100 W [2010: 2 M]

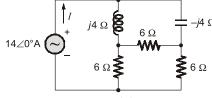

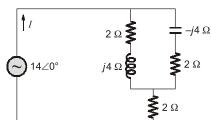

In the circuit shown below, the current I is equal to

- (a) 1.4∠0° A

- (b) 2.0∠0° A

- (c) 2.8∠0° A

- (d) 3.2∠0° A [2011 : 2 M]

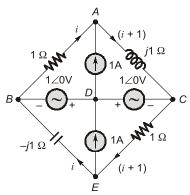

1.31 In the circuit shown below, the current through the inductor is

- (a)  $\frac{2}{1+i}$  A

- (c)  $\frac{1}{1+i}$  A

[2012:1 M]

- 1.32 The average power delivered to an impedance  $(4-j3)\Omega$  by a current 5 cos(100  $\pi$  t + 100)A is

- (a) 44.2 W

- (b) 50 W

- (c) 62.5 W

- (d) 125 W

[2012:1 M]

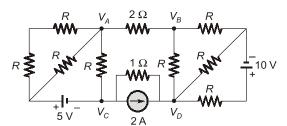

**1.33** If  $V_A - V_B = 6$  V, then  $V_C - V_D$  is

- (a) -5 V

- (b) 2 V

- (c) 3 V

- (d) 6 V

[2012 : 2 M]

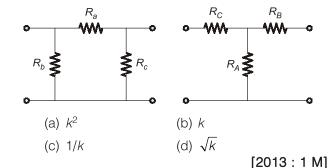

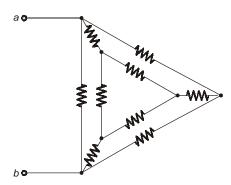

1.34 Consider a delta connection of resistors and its equivalent star connection as shown below. If all elements of the delta connection are scaled by a factor k, k > 0, the elements of the corresponding star equivalent will be scaled by a factor of

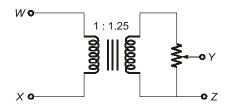

1.35 The following arrangement consists of an ideal transformer and an attenuator which attenuates by a factor of 0.8. An ac voltage  $V_{WX_1} = 100 \text{ V}$  is applied across WX to get an open circuit voltage  $V_{YZ_1}$  across YZ. Next, an ac voltage  $V_{YZ_2}$  = 100 V is applied across YZ to get an open circuit voltage  $V_{\rm WX_2}$  across WX. Then,  $V_{\rm YZ_1}/V_{\rm WX_1}$ ,  $V_{\rm WX_2}/V_{\rm YZ_2}$  are respectively,

- (a) 125/100 and 80/100

- (b) 100/100 and 80/100

- (c) 100/100 and 100/100

- (d) 80/100 and 80/100

[2013:2 M]

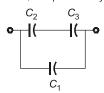

**1.36** Three capacitors  $C_1$ ,  $C_2$  and  $C_3$  whose values are 10  $\mu$ F, 5  $\mu$ F, and 2  $\mu$ F respectively, have breakdown voltages of 10 V, 5 V and 2 V respectively. For the interconnection shown below, the maximum safe voltage in volts that can be applied across the combination, and the corresponding total charge in µC stored in the effective capacitance across the terminals are, respectively

- (a) 2.8 and 36

- (b) 7 and 119

- (c) 2.8 and 32

- (d) 7 and 80

[2013:2 M]

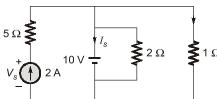

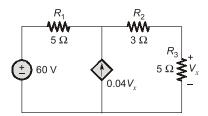

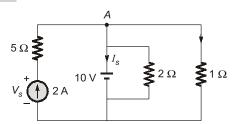

#### Common Data For Questions 1.37 and 1.38:

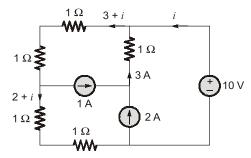

Consider the following figure:

- **1.37** The current  $I_s$  in Amps in the voltage source, and voltage  $V_s$  in volts across the current source respectively, are

- (a) 13, -20

- (b) 8, -10

- (c) -8, 20

- (d) -13, 20 **[2013 : 2 M]**

- **1.38** The current in the 1  $\Omega$  resistor in Amps is

- (a) 2

- (b) 3.33

- (c) 10

- (d) 12

[2013 : 2 M]

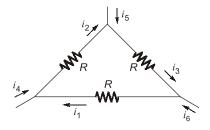

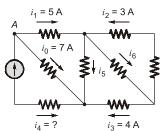

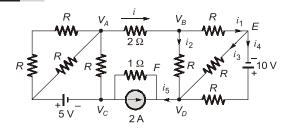

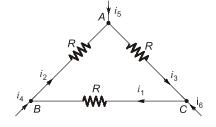

Consider the configuration shown in the figure 1.39 which is a portion of a larger electrical network

For  $R = 1 \Omega$  and currents  $i_1 = 2 A$ ,  $i_2 = -1 A$ ,  $i_5 = -4$  A, which one of the following is TRUE?

- (a)  $i_6 = 5 \text{ A}$

- (b)  $i_3 = -4 \text{ A}$

- (c) Data is sufficient to conclude that the supposed currents are impossible

- (d) Data is insufficient to identify the currents  $i_2$ ,  $i_3$  and  $i_6$

[2014: 1 M, Set-1]

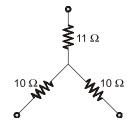

**1.40** A Y-network has resistances of 10  $\Omega$  each in two of its arms, while the third arm has a resistance of 11  $\Omega$ . In the equivalent  $\Delta$ -network, the lowest value (in  $\Omega$ ) among the three resistances is \_\_\_\_

[2014: 2 M, Set-1]

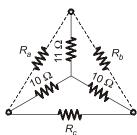

**1.41** For the Y-network shown in the figure, the value of  $R_1$  (in  $\Omega$ ) in the equivalent D-network is \_\_\_\_\_.

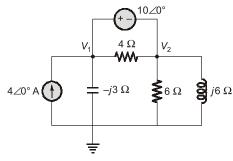

1.42 In the circuit shown in the figure, the value of node voltage  $V_2$  is

- (a) 22 + j2 V

- (b) 2 + j22 V

- (c) 22 j2 V

- (d) 2 j22 V

[2014: 2 M, Set-3]

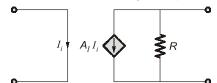

1.43 The circuit shown in the figure represents a

- (a) voltage controlled voltage source

- (b) voltage controlled current source

- (c) current controlled current source

- (d) current controlled voltage source

[2014: 1 M, Set-4]

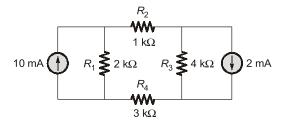

1.44 The magnitude of current (in mA) through the resistor  $R_2$  in the figure shown is\_

[2014: 1 M, Set-4]

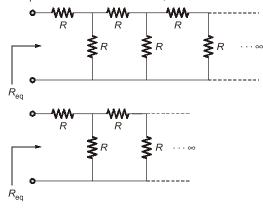

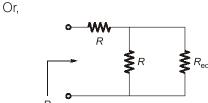

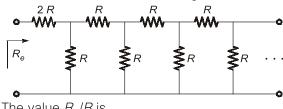

1.45 The equivalent resistance in the infinite ladder network shown in the figure, is  $R_e$ .

The value  $R_{\rho}/R$  is

[2014: 2 M, Set-4]

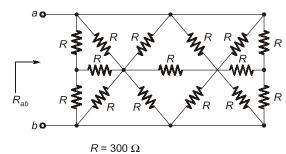

**1.46** In the network shown in the figure, all resistors are identical with  $R = 300 \Omega$ . The resistance  $R_{ab}$ (in  $\Omega$ ) of the network is \_\_\_\_\_

[2015: 1 M, Set-1]

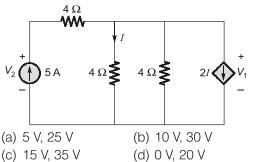

**1.47** In the given circuit, the values of  $V_1$  and  $V_2$ respectively are

[2015: 1 M, Set-1]

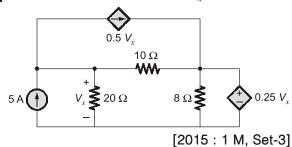

**1.48** In the circuit shown, the voltage  $V_r$  (in Volts) is \_\_\_\_.

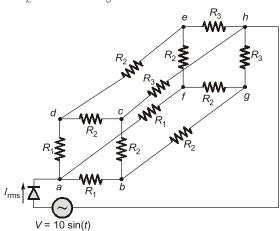

**1.49** An AC voltage source  $V = 10 \sin(t)$  volts is applied to the following network. Assume that  $R_1 = 3 \text{ k}\Omega$ ,  $R_2 = 6 \text{ k}\Omega$  and  $R_3 = 9 \text{ k}\Omega$ , and that the diode is ideal.

RMS current  $I_{rms}$  (in mA) through the diode is \_\_\_\_\_.

[2016: 2 M, Set-1]

1.50 In the given circuit, each resistor has a value equal to 1  $\Omega$ .

What is the equivalent resistance across the terminals *a* and *b*?

- (a)  $1/6 \Omega$

- (b)  $1/3 \Omega$

- (c)  $9/20 \Omega$

- (d)  $8/15 \Omega$

[2016: 2 M, Set-2]

In the circuit shown in the figure, the magnitude of the current (in amperes) through  $R_2$  is \_\_\_\_

[2016: 2 M, Set-2]

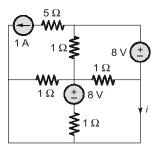

**1.52** In the figure shown, the current *i* (in ampere) is \_\_\_\_.

[2016 : 2 M, Set-3]

in series with a parallel combination of resistance A in series with a parallel combination of resistances B and C. Three resistors of value  $10 \Omega$ ,  $5 \Omega$ ,  $2 \Omega$  are provided. Consider all possible permutations of the given resistors into the positions A, B, C and identify the configurations with maximum possible overall resistance, and also the ones with minimum possible overall resistance. The ratio of maximum to minimum values of the resistances (up to second decimal place) is

[2017:1 M, Set-2]

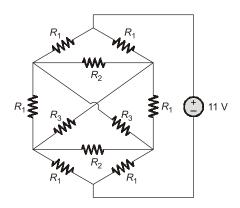

**1.54** Consider the network shown below with  $R_1 = 1 \Omega$ ,  $R_2 = 2 \Omega$  and  $R_3 = 3 \Omega$ . The network is connected to a constant voltage source of 11 V.

The magnitude of the current (in amperes, accurate to two decimal places) through the source is \_\_\_\_\_.

[2018 : 2 M]

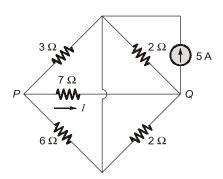

**1.55** Consider the circuit shown in the figure.

The current I flowing through the 7  $\Omega$  resistor between P and Q (rounded off to one decimal place) is \_\_\_\_\_ A.

[2021:1 M]

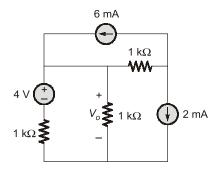

**1.56** Consider the circuit shown in the figure.

The value of  $V_o$  (rounded off to one decimal place) is  $V_o$

[2021:1 M]

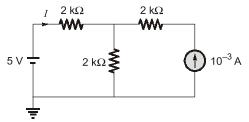

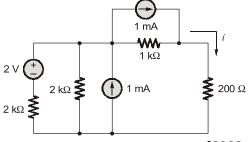

**1.57** The current *I* in the circuit shown is \_

- (a)  $1.25 \times 10^{-3} \text{ A}$

- (b)  $0.75 \times 10^{-3} \text{ A}$

- (c)  $-0.5 \times 10^{-3}$  A

- (d)  $1.16 \times 10^{-3} \text{ A}$

[2022:1 M]

1.58 Consider the circuit shown in the figure. The current I flowing through the 10  $\Omega$  resistor is \_

- (c) 0.1 A

- (d) -0.1 A

[2022:1 M]

**1.59** In the circuit shown below, the current i flowing through 200  $\Omega$  resistor is \_\_\_\_ mA. (rounded off to two decimal places).

[2023:1 M]

**1.60** In the given circuit, the current  $I_{x}$  (in mA) is \_\_\_\_\_.

| Answers B | asics of | Network | <b>Analysis</b> |

|-----------|----------|---------|-----------------|

|-----------|----------|---------|-----------------|

| 1.1  | (d) | 1.2  | (b)   | 1.3  | (a)    | 1.4  | (d)     | 1.5  | (a)     | 1.6  | (b)   | 1.7  | (c) |

|------|-----|------|-------|------|--------|------|---------|------|---------|------|-------|------|-----|

| 1.8  | (b) | 1.9  | (c)   | 1.10 | (d)    | 1.11 | (d)     | 1.12 | (a)     | 1.13 | (d)   | 1.14 | (c) |

| 1.15 | (a) | 1.16 | (d)   | 1.17 | (a)    | 1.18 | (d)     | 1.19 | (a)     | 1.20 | (a)   | 1.21 | (*) |

| 1.22 | (d) | 1.23 | (d)   | 1.24 | (d)    | 1.25 | (b)     | 1.26 | (c)     | 1.27 | (a)   | 1.28 | (c) |

| 1.29 | (a) | 1.30 | (b)   | 1.31 | (c)    | 1.32 | (b)     | 1.33 | (a)     | 1.34 | (b)   | 1.35 | (b) |

| 1.36 | (c) | 1.37 | (d)   | 1.38 | (c)    | 1.39 | (a)     | 1.40 | (29.09) | 1.41 | (10)  | 1.42 | (d) |

| 1.43 | (c) | 1.44 | (2.8) | 1.45 | (2.62) | 1.46 | (100)   | 1.47 | (a)     | 1.48 | (8)   | 1.49 | (1) |

| 1.50 | (d) | 1.51 | (5)   | 1.52 | (-1)   | 1.53 | (2.143) | 1.54 | (8)     | 1.55 | (0.5) | 1.56 | (1) |

| 1 57 | (b) | 1.58 | (b)   | 1 59 | (1.36) | 1 60 | (2)     |      |         |      |       |      |     |

#### **Basics of Network Analysis Explanations**

#### 1.1 (d)

$$L = L_1 + L_2 \pm 2 M = L_1 + L_2 \pm 2 k \sqrt{L_1 L_2}$$

$$L = 2 + 2 \pm 2(0.1)\sqrt{2 \times 2} = 4 \pm 0.4$$

$$L = 3.6 \text{ H and } 4.4 \text{ H}$$

#### 1.2 (b)

at node

$$A$$

$i_0 + i_1 + i_4 = 0$

$7 + 5 + i_4 = 0$

$i_4 = -12 \text{ A}$

Apply KCL

#### 1.3 (a)

Apply KVL,

$$V + 5 - 4 - 4 = 0$$

$V = 3 \text{ V}$

#### 1.4 (d)

$$V = V_{2A} + 2 \times 2 + 5 = V_{2A} + 9$$

Since the voltage of 2 A current source is not known.

So, it is not possible to find the value of voltage V.

#### 1.5 (a)

Voltage in parallel is always equal.

#### 1.6 (b)

The bridge is balanced

$$Z_{\text{eq}} = (2 \parallel 4) + (2 \parallel 4)$$

$$Z_{\text{eq}} = \frac{2 \times 4}{2 + 4} + \frac{2 \times 4}{2 + 4} = \frac{4}{3} + \frac{4}{3} = \frac{8}{3} \Omega$$

#### 1.7 (c)

Using source transformation,

#### 1.8 (b)

The nodal or mesh method is based on KCL and Ohm's law.

#### 1.9 (c)

Apply superposition theorem

For 1 volt source

$$V_{ab_1} = 1 \times \frac{2}{2+2} = 0.5 \text{ V}$$

For 3 A source.

$$V_{ab3} = 3 \times \left(\frac{2}{2+2}\right) \times 2 = 3 \text{ V}$$

$V_{ab} = V_{ab1} + V_{ab3} = 0.5 + 3 = 3.5 \text{ V}$

#### 1.10 (d)

$$R_1 = \frac{5 \times 30}{5 + 30 + 15} = 3$$

;  $R_2 = \frac{15 \times 5}{50} = 1.5$

$R_3 = \frac{15 \times 30}{50} = 9$

#### 1.11 (d)

Applying KCL at the node (1),  $e^{at} + e^{bt} = i_t(t)$  $\Rightarrow v(t) = L \frac{d}{dt} [e^{at} + e^{bt}] = ae^{at} + be^{bt}$

#### 1.12 (a)

#### 1.13 (d)

Since diode is forward bias it is taken as short circuit. Applying KCL,

$$\frac{V-4}{2} + \frac{V}{2} + \frac{V+2}{2} = 0$$

$$3 V = 2 \qquad \Rightarrow V = 2/3$$

$$\Rightarrow \qquad V_o = -V = -\frac{2}{3}$$

#### 1.14 (c)

Applying KCL,

$$\frac{e_o - 12}{4} + \frac{e_o}{4} + \frac{e_o}{4} = 0$$

$\Rightarrow 3e_o = 12 \quad \therefore \quad e_o = 4 \text{ V}$

#### 1.15 (a)

$$Z_{\Delta} = 3Z_{\gamma} \quad \Rightarrow \sqrt{3} Z_{\Delta} = 3Z_{\gamma} \quad ; \quad Z_{\gamma} = \frac{Z_{\Delta}}{\sqrt{3}}$$

#### 1.16 (d)

Applying source conversion

$$\frac{e_o - 80}{12} + \frac{e_o}{12} + \frac{e_o - 16}{6} = 0$$

$$4e_o = 112$$

$$e_o = \frac{112}{4} = 28 \text{ V}$$

#### 1.17 (a)

Applying KVL,

$$20 - 5I - 5\left(I + \frac{V_1}{5}\right) = 0$$

$20 - 10I - 20 = 0$

$\Rightarrow I = 0$

.. Only dependent source acts.

$$\frac{V_1}{5} = 4 \text{ A}$$

Power delivered =  $I^2R$  = 16 × 5 = 80 W

#### 1.18 (d)

$$3V_{p}I_{p}\cos\theta = 1500$$

$$3\left(\frac{V_{L}}{\sqrt{3}}\right)\left(\frac{V_{L}}{\sqrt{3}Z_{L}}\right)\cos\theta = 1500$$

$$Z_{L} = \frac{V_{L}^{2} \cdot \cos\theta}{1500} = \frac{400^{2} \times 0.844}{1500} = 90 \Omega$$

$$\theta = \cos^{-1}(0.844) = 32.44$$

As power factor is leading, load is capacitive so angle will be negative.

$$\theta = -32.44^{\circ}$$

#### 1.19 (a)

As voltage at 1 node is known

∴ using nodal analysis only 3 equations required.

#### 1.20 (a)

$$V_{ab} = \frac{i}{3} \times 1 + \frac{i}{6} \times 1 + \frac{i}{3} \times 1$$

$$\Rightarrow R_{eq} = \frac{V_{ab}}{i} = \frac{5}{6} \Omega$$

#### 1.21 (\*)

Question is incomplete as  $L_1$  and  $L_2$  are not given.

#### 1.22 (d)

Hence, the charging requires constant current source of 3 mA for 2 msec.

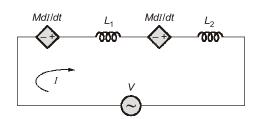

#### 1.23 (d)

If current enters the dotted terminals of coil 1 then a voltage is developed across coil 2 whose higher potential is at dotted terminals.

$$V = \frac{-MdI}{dt} + \frac{L_1dI}{dt} - \frac{MdI}{dt} + L_2 \frac{dI}{dt}$$

$$= (L_1 + L_2 - 2M) \frac{dI}{dt} \qquad V = L_{eq} \frac{dI}{dt}$$

#### 1.24 (d)

$$H(s) = \frac{\frac{1}{sC}}{R + sL + \frac{1}{sC}} = \frac{1}{s^2LC + sCR + 1}$$

$$= \frac{1}{s^2(10 \times 10^{-3} \times 100 \times 10^{-6}) + s(10 \times 10^3 \times 100 \times 10^{-6}) + 1}$$

$$H(s) = \frac{1}{10^{-6}s^2 + s + 1} = \frac{10^6}{s^2 + 10^6s + 10^6}$$

#### 1.25 (b)

$$X = X_1 + X_2 + X_3 + 2X_m - 2X_m$$

=  $(j5 + j2 + j2 + j20 - j20) \Omega$

=  $j9 \Omega$  (one additive & other subtractive)

#### 1.26 (c)

$$V_a = 5 \qquad (R_1 = R_2)$$

$$V_b = \frac{R_3}{R_3 + R_4} \times 10 = \frac{1.1}{2.1} \times 10$$

$V = V_a - V_b = -0.238 \text{ V}$

#### 1.27 (a)

Since, the power is absorbed by 60 V source

#### 1.28 (c)

$$P = VI$$

Energy =  $P \cdot t = V \cdot |t| = (V \cdot t)|$

$$I = 2A \quad \text{(given)}$$

$$V \cdot t = \text{Area under } V - t \text{ curve}$$

$$V \cdot t = \left(\frac{1}{2} \times 2 \times 600\right) + (10 \times 600)$$

$$= 600 + 6000$$

$$V \cdot t = 6600$$

$$E = (6600) \times 2 = 13200 = 13.2 \text{ kJ}$$

#### 1.29 (a)

Applying KVL in outer loop,

$$(3+i)2 + (2+i)2 = 10$$

$$\Rightarrow 6+2i+4+2i = 10$$

$$\Rightarrow 4i = 0$$

$$\Rightarrow i = 0$$

Power supplied by the voltage source,

$$P = Vi = 10 \times 0 = 0 \text{ W}$$

#### 1.30 (b)

Converting delta into star, the circuit can be redrawn as below:

Equivalent impedance of the circuit,

$$Z = (2 + j4) | | (2 - j4) + 2$$

$$\Rightarrow Z = \frac{(2 + j4)(2 - j4)}{2 + j4 + 2 - j4} + 2 = \frac{4 + 16}{4} + 2 = 7\Omega$$

Therefore

Current,

$$I = \frac{14\angle 0^{\circ}}{7} = 2\angle 0^{\circ} A$$

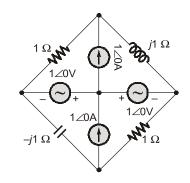

#### 1.31 (c)

According to KCL at node *D* there will be no current in voltage sources.

According to KCL at node *A* current through inductor will be

$$i_1 = i + 1$$

...(1)

Applying KVL in loop ACDBA we have

$$1 \times i + (i+1) j + 1 \angle 0 - 1 \angle 0 = 0$$

$$i + (i+1)j = 0$$

$$(1+j)i = -j$$

$$i = \frac{-j}{1+j} \qquad ...(2)$$

Therefore from (1) and (2) we have

$$i_1 = i + 1 = \frac{-j}{j+1} + 1 = \frac{1}{1+j}$$

#### 1.32 (b)

Average power is same as RMS power.

$$P = I_{\text{rms}}^2 R = \left(\frac{5}{\sqrt{2}}\right)^2 \times 4 = \frac{25}{2} \times 4 = 50 \text{ W}$$

**Note:** Power is consumed only by resistance i.e. by real part of impedance.

#### 1.33 (a)

$$i = \frac{V_A - V_B}{2} = \frac{6}{2} = 3 \text{ A} \quad ...(i)$$

KCL at node B, we have

$$\begin{split} i &= i_2 + i_1 \\ i_2 + i_1 &= 3 \; \text{A} \end{split} \qquad ...(ii) \label{eq:i2}$$

KCL at node E, we have

$$i_1 = i_3 + i_4$$

...(iii)

KCL at node D we have

$$i_5 = i_2 + i_3 + i_4 = i_2 + i_1 = 3 \text{ A}$$

KCL at node F, we have

$$i_6+2+i_5=0 \\ i_6=-2-i_5=-5 \text{ A} \\ \text{So,} \qquad V_C-V_D=1\times i_6=-5 \text{ V}$$

#### 1.34 (b)

$$\begin{split} R_{A} &= \frac{R_{b}R_{c}}{R_{a} + R_{b} + R_{c}} \\ R'_{a} &= kR_{a}; \quad R'_{b} = kR_{b}; \quad R'_{c} = kR_{c} \\ R'_{A} &= \frac{kR_{b} \cdot kR_{c}}{kR_{a} + kR_{b} + kR_{c}} = \frac{k^{2}R_{b}R_{c}}{k(R_{A} + R_{b} + R_{c})} \\ &= k \times \frac{R_{b}R_{c}}{R_{a} + R_{b} + R_{c}} \\ R'_{A} &= kR_{A} \end{split}$$

#### 1.35 (b)

$$V_{YZ_1} = 100 \times 1.25 \times 0.8 = 100 \text{ V}$$

In second case, when 100 V is applied at YZ terminals, this whole 100 V will appear across the secondary winding.

Hence,

$$V_{WX_2} = \frac{100}{1.25} = 80 \text{ V}$$

$$\Rightarrow \frac{Y_{YZ_1}}{Y_{WX_1}} = \frac{100}{100}, \frac{V_{WX_2}}{V_{YZ_2}} = \frac{80}{100}$$

#### 1.36 (c)

$$Q = CV$$

$Q_1 = C_1 V_1 = 10 \times 10^{-6} \times 10 = 100 \,\mu\text{C}$

$Q_2 = C_2 V_2 = 5 \times 10^{-6} \times 5 = 25 \,\mu\text{C}$

$Q_3 = C_3 V_3 = 2 \times 10^{-6} \times 2 = 4 \,\mu\text{C}$

Capacitors  $C_2$  and  $C_3$  are in series.

In series charge is same.

So, the maximum charge on  $C_2$  and  $C_3$  will be minimum of  $(Q_2, Q_3) = \min(25 \, \mu\text{C}, 4 \, \mu\text{C}) = 4 \, \mu\text{C} = Q_{23}$ . In series the equivalent capacitance of  $C_2$  and  $C_3$  is

$$C_{23} = \frac{C_2 C_3}{C_2 + C_2} = \frac{5 \times 2}{5 + 2} = \frac{10}{7} \mu F$$

So, the equivalent voltage

$$V_{23} = \frac{Q_{23}}{C_{23}} = \frac{4 \times 10^{-6}}{\frac{10}{7} \times 10^{-6}} = \frac{28}{10} = 2.8 \text{ V}$$

In parallel, the voltage is same.

$$V_1 = V_{23} = 2.8 \text{ V}$$

Charge in capacitor C<sub>1</sub>,

$$Q_1 = C_1 V_1 = 10 \times 10^{-6} \times 2.8 = 28 \ \mu\text{C}$$

In parallel, the total charge

$$Q = Q_1 + Q_{23} = 4 + 28 = 32 \,\mu\text{C}$$

#### 1.37 (d)

Voltage across 1  $\Omega$  resistance,

$$V_1 = 10 \text{ V}$$

Current through 1  $\Omega$  resistance,

$$I_1 = \frac{10}{1} = 10$$

Amp.

Voltage across  $2 \Omega$  resistance,

$$V_2 = 10 \text{ V}$$

Current through 2  $\Omega$  resistance,

$$I_2 = \frac{10}{2} = 5 \text{ Amp.}$$

Apply KCL at node A,

$$-2 + I_s + I_2 + I_1 = 0$$

$I_s = 2 - I_1 - I_2 = 2 - 10 - 5$

$I_s = -13 \text{ Amp}$

Voltage at node A,

$$V_A = 10 \text{ V}$$

$V_S - 10 = 10 \text{ V}$

$V_S = 10 + 10 = 20 \text{ V}$

#### 1.38 (c)

The current in the 1  $\Omega$  resistor

$$I_1 = \frac{10}{1} = 10$$

Amp.

#### 1.39 (a)

Given data:

$$i_1 = 2 \text{ A}$$

,  $i_4 = -1 \text{ A}$ ,  $i_5 = -4 \text{ A}$

$R = 1 \Omega$

To calculate:

$$i_6 = ?$$

Using KVL at all the three nodes we get,

At node A,

$$i_5 - i_3 + i_2 = 0$$

...(i)

At node B,

$$i_4 + i_1 - i_2 = 0$$

...(ii)

At node C,

$$i_6 + i_3 - i_1 = 0$$

...(iii)

$i_6+i_3-i_1=0 \qquad \qquad ... \mbox{(iii)}$  By putting the value of  $i_3$  and  $i_2$  from equation (i) and (ii) in equation (iii) we get,

$$i_{6} + (i_{2} + i_{5}) - i_{1} = 0$$

$$i_{6} + (i_{1} + i_{4} + i_{5}) - i_{1} = 0$$

$$\vdots \quad i_{6} + (2 - 1 - 4) - 2 = 0$$

$$i_{6} = 5 \text{ A}$$

#### 1.40 (29.09)

According to the question

The equivalent  $\Delta$ -network of the above Y-network is

Here,

$$R_a=10+11+\frac{10\times11}{10}=32\,\Omega$$

$$R_b=10+11+\frac{10\times11}{10}=32\,\Omega$$

$$R_c=10+10+\frac{10\times10}{11}=29.09\,\Omega$$

Hence, the lowest value among the three resistances is 29.09  $\Omega$ .

#### 1.41 (10)

Using star-delta conversions,

The value of  $R_1$  is given by

$$=5+3+\frac{5\times3}{7.5}=10$$

#### 1.42 (d)

Using the concept of super node, we get

$$V_1 - V_2 = 10 \angle 0^\circ$$

...(i)

=  $\frac{V_1}{-3j} + \frac{V_2}{6j} + \frac{V_2}{6} = 4 \angle 0^\circ$  ...(ii)

$$= \frac{-2V_1 + V_2 + jV_2}{6j} = 4 \angle 0^{\circ} \qquad ...(iii)$$

From equation (i) and (iii)

$$V_2 = \frac{20 + j24}{(-1+j)} = \frac{31.241 \angle 50.194}{\sqrt{2} \angle 135^\circ}$$

$$= 22.091 \angle -84.806$$

$$V_2 = 2 - 22j$$

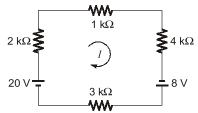

#### 1.44 (2.8)

or

Using source transformation, we get,

Applying KVL in above circuit, we get, 20 - 2I - I - 4I + 8 - 3I = 0or 28 = 10Ior I = 2.8 mA

#### 1.45 (2.62)

For an infinite ladder network, if all the resistance are comprises of same value R, then